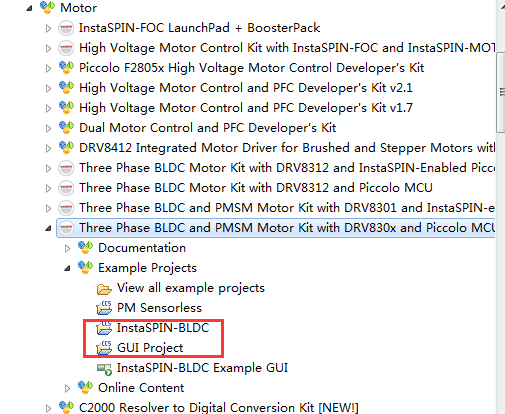

TI官方开发板: DRV8301-HC-C2-KIT,控制卡dsp是F28035,电机驱动芯片是DRV8301,导入controlsuit默认的示例工程

InstaSPIN-BLDC和InstaSPIN_BLDC。

GUI工程默认就是从flash启动,而instaSPIN-BLDC工程默认从ram启动,现在需要instaSPIN-BLDC工程也需要从flash启动,对instaSPIN-BLDC工程做了几处更改:

1.增加2个按键中断,中断函数名称

void xint1_isr(void);

void xint2_isr(void);

2.在dac中断里面读取了电位器dac的数值,并且进行了简单的赋值操作

现在在ram中运行良好,没什么异常。

参照GUI工程从flash启动,首先在工程里面定义编译宏FLASH,将自带的cmd文件用gui中的cmd文件覆盖,并且对工程进行了修改,

修改的主要位置为:

BLDC_Int.c中

#ifdef FLASH #pragma CODE_SECTION(MainISR,"ramfuncs"); #pragma CODE_SECTION(xint1_isr,"ramfuncs"); #pragma CODE_SECTION(xint2_isr,"ramfuncs"); #pragma DATA_SECTION(InstaSPIN_BLDC1,"BLDC"); void MemCopy(); void InitFlash(); #endif

对cmd文件也进行了修改,修改后的cmd文件为:

/*==================================================================================*/

/* User specific Linker command file for running from FLASH */

/*==================================================================================*/

/* FILE: F28035_FLASH_DRV8412GUI.CMD*/

/**/

/* Description: Linker command file for User custom sections targetted to run*/

/* from FLASH.*/

/**/

/* Target: TMS320F28035*/

/**/

/* Version: 1.00 */

/**/

/*----------------------------------------------------------------------------------*/

/* Copyright Texas Instruments �2009*/

/*----------------------------------------------------------------------------------*/

/* Revision History:*/

/*----------------------------------------------------------------------------------*/

/* Date| Description*/

/*----------------------------------------------------------------------------------*/

/* 4/13/09 | Release 1.0 New release.*/

/*----------------------------------------------------------------------------------*/

/* Define the memory block start/length for the F28035PAGE 0 will be used to organize program sectionsPAGE 1 will be used to organize data sectionsNotes:Memory blocks on F2803x are uniform (ie samephysical memory) in both PAGE 0 and PAGE 1.That is the same memory region should not bedefined for both PAGE 0 and PAGE 1.Doing so will result in corruption of programand/or data.L0 memory block is mirrored - that isit can be accessed in high memory or low memory.For simplicity only one instance is used in thislinker file.Contiguous SARAM memory blocks or flash sectors can bebe combined if required to create a larger memory block.

*/

MEMORY

{

/* Note that the memory allocation below does not create sections as necessary forthe CLA on the F2803x.

*/

PAGE 0:

progRAM: origin = 0x008000, length = 0x001000 /* on-chip RAM (L0-L2)*/

OTP: origin = 0x3D7800, length = 0x000400/* on-chip OTP */

FLASHH: origin = 0x3E8000, length = 0x002000/* on-chip FLASH */

FLASHG: origin = 0x3EA000, length = 0x002000/* on-chip FLASH */

FLASHF: origin = 0x3EC000, length = 0x002000/* on-chip FLASH */

FLASHE: origin = 0x3EE000, length = 0x002000/* on-chip FLASH */

FLASHD: origin = 0x3F0000, length = 0x002000/* on-chip FLASH */

FLASHC: origin = 0x3F2000, length = 0x002000/* on-chip FLASH */

FLASHB: origin = 0x3F4000, length = 0x002000/* on-chip FLASH */

FLASHA: origin = 0x3F6000, length = 0x001F80/* on-chip FLASH */

CSM_RSVD: origin = 0x3F7F80, length = 0x000076/* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN: origin = 0x3F7FF6, length = 0x000002/* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL: origin = 0x3F7FF8, length = 0x000008/* Part of FLASHA. CSM password locations in FLASHA */

IQTABLES: origin = 0x3FE000, length = 0x000B50/* IQ Math Tables in Boot ROM */

IQTABLES2: origin = 0x3FEB50, length = 0x00008C/* IQ Math Tables in Boot ROM */

IQTABLES3: origin = 0x3FEBDC, length = 0x0000AA/* IQ Math Tables in Boot ROM */

BOOTROM: origin = 0x3FF27C, length = 0x000D44/* Boot ROM */

RESET: origin = 0x3FFFC0, length = 0x000002/* part of boot ROM */

VECTORS: origin = 0x3FFFC2, length = 0x00003E/* part of boot ROM */

PAGE 1 :

BOOT_RSVD: origin = 0x000000, length = 0x000050/* Part of M0, BOOT rom will use this for stack */

RAMM0: origin = 0x000050, length = 0x0003B0/* on-chip RAM block M0 */ RAMM1: origin = 0x000400, length = 0x00400/* on-chip RAM block M1 */

/* RAMM1a: origin = 0x000400, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1b: origin = 0x000500, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1c: origin = 0x000600, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1d: origin = 0x000700, length = 0x00100*//* on-chip RAM block M1 */

dlog1RAM : origin = 0x009000, length = 0x00200

dlog2RAM : origin = 0x009200, length = 0x00200

dlog3RAM : origin = 0x009400, length = 0x00200

/* dataRAM: origin = 0x009000, length = 0x000F00*//* data RAM (L3) */

dataRAM: origin = 0x009600, length = 0x000900/* data RAM (L3) */

BLDCRAM: origin = 0x009F00, length = 0x000100/* data RAM (L3) */

CLA_CPU_MSGRAM : origin = 0x001480, length = 0x000080 /* CLA-R/W, CPU-R message RAM */

CPU_CLA_MSGRAM : origin = 0x001500, length = 0x000080 /* CPU-R/W, CLA-R message RAM */

}

SECTIONS

{/* Allocate program areas: */.cinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.pinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.text: >> FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0codestart: > BEGINPAGE = 0ramfuncs: LOAD = FLASHD,RUN = progRAM,LOAD_START(_RamfuncsLoadStart),LOAD_END(_RamfuncsLoadEnd),RUN_START(_RamfuncsRunStart),PAGE = 0csmpasswds: > CSM_PWLPAGE = 0csm_rsvd: > CSM_RSVDPAGE = 0/* Allocate uninitalized data sections: */.stack: > RAMM0,PAGE = 1.ebss: > dataRAM,PAGE = 1.esysmem: > dataRAM,PAGE = 1DLOG: > dataRAM,PAGE = 1

/*DLOG1: > RAMM1a,PAGE = 1*/

/*DLOG2: > RAMM1b,PAGE = 1*/

/*DLOG3: > RAMM1c,PAGE = 1*/

/*DLOG4: > RAMM1d,PAGE = 1*/DLOG1: > dlog1RAM,PAGE = 1DLOG2: > dlog2RAM,PAGE = 1DLOG3: > dlog3RAM,PAGE = 1BLDC: > BLDCRAM,PAGE = 1/* Initalized sections go in Flash *//* For SDFlash to program these, they must be allocated to page 0 */.econst: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0.switch: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Allocate IQ math areas: */IQmath: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Math Code */IQmathTables: > IQTABLESPAGE = 0, TYPE = NOLOAD/* Math Tables In ROM */Cla1ToCpuMsgRAM: > CLA_CPU_MSGRAM PAGE = 1CpuToCla1MsgRAM: > CPU_CLA_MSGRAM PAGE = 1.reset: > RESET,PAGE = 0, TYPE = DSECTvectors: > VECTORSPAGE = 0, TYPE = DSECT/* Uncomment the section below if calling the IQNexp() or IQexp()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables2: > IQTABLES2, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)}*//* Uncomment the section below if calling the IQNasin() or IQasin()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables3: > IQTABLES3, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)}*/

}

编译有一个warning,

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQ24div.obj>":

compatibility cannot be determined

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQmathTables.obj>":

compatibility cannot be determined

说是编译器版本问题。

现在能顺利下载,功能正常,但是断电重启后程序不运行,请问如何解决????

囧:

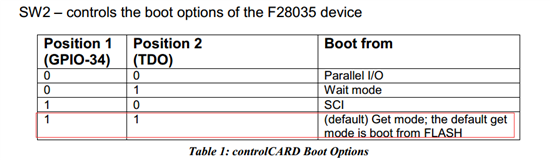

warining不影响程序运行,断电后重启不行可能是bootmode的设置,你看看GPIO34,和GPIO37现在是什么位置,应该是11

TI官方开发板: DRV8301-HC-C2-KIT,控制卡dsp是F28035,电机驱动芯片是DRV8301,导入controlsuit默认的示例工程

InstaSPIN-BLDC和InstaSPIN_BLDC。

GUI工程默认就是从flash启动,而instaSPIN-BLDC工程默认从ram启动,现在需要instaSPIN-BLDC工程也需要从flash启动,对instaSPIN-BLDC工程做了几处更改:

1.增加2个按键中断,中断函数名称

void xint1_isr(void);

void xint2_isr(void);

2.在dac中断里面读取了电位器dac的数值,并且进行了简单的赋值操作

现在在ram中运行良好,没什么异常。

参照GUI工程从flash启动,首先在工程里面定义编译宏FLASH,将自带的cmd文件用gui中的cmd文件覆盖,并且对工程进行了修改,

修改的主要位置为:

BLDC_Int.c中

#ifdef FLASH #pragma CODE_SECTION(MainISR,"ramfuncs"); #pragma CODE_SECTION(xint1_isr,"ramfuncs"); #pragma CODE_SECTION(xint2_isr,"ramfuncs"); #pragma DATA_SECTION(InstaSPIN_BLDC1,"BLDC"); void MemCopy(); void InitFlash(); #endif

对cmd文件也进行了修改,修改后的cmd文件为:

/*==================================================================================*/

/* User specific Linker command file for running from FLASH */

/*==================================================================================*/

/* FILE: F28035_FLASH_DRV8412GUI.CMD*/

/**/

/* Description: Linker command file for User custom sections targetted to run*/

/* from FLASH.*/

/**/

/* Target: TMS320F28035*/

/**/

/* Version: 1.00 */

/**/

/*----------------------------------------------------------------------------------*/

/* Copyright Texas Instruments �2009*/

/*----------------------------------------------------------------------------------*/

/* Revision History:*/

/*----------------------------------------------------------------------------------*/

/* Date| Description*/

/*----------------------------------------------------------------------------------*/

/* 4/13/09 | Release 1.0 New release.*/

/*----------------------------------------------------------------------------------*/

/* Define the memory block start/length for the F28035PAGE 0 will be used to organize program sectionsPAGE 1 will be used to organize data sectionsNotes:Memory blocks on F2803x are uniform (ie samephysical memory) in both PAGE 0 and PAGE 1.That is the same memory region should not bedefined for both PAGE 0 and PAGE 1.Doing so will result in corruption of programand/or data.L0 memory block is mirrored - that isit can be accessed in high memory or low memory.For simplicity only one instance is used in thislinker file.Contiguous SARAM memory blocks or flash sectors can bebe combined if required to create a larger memory block.

*/

MEMORY

{

/* Note that the memory allocation below does not create sections as necessary forthe CLA on the F2803x.

*/

PAGE 0:

progRAM: origin = 0x008000, length = 0x001000 /* on-chip RAM (L0-L2)*/

OTP: origin = 0x3D7800, length = 0x000400/* on-chip OTP */

FLASHH: origin = 0x3E8000, length = 0x002000/* on-chip FLASH */

FLASHG: origin = 0x3EA000, length = 0x002000/* on-chip FLASH */

FLASHF: origin = 0x3EC000, length = 0x002000/* on-chip FLASH */

FLASHE: origin = 0x3EE000, length = 0x002000/* on-chip FLASH */

FLASHD: origin = 0x3F0000, length = 0x002000/* on-chip FLASH */

FLASHC: origin = 0x3F2000, length = 0x002000/* on-chip FLASH */

FLASHB: origin = 0x3F4000, length = 0x002000/* on-chip FLASH */

FLASHA: origin = 0x3F6000, length = 0x001F80/* on-chip FLASH */

CSM_RSVD: origin = 0x3F7F80, length = 0x000076/* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN: origin = 0x3F7FF6, length = 0x000002/* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL: origin = 0x3F7FF8, length = 0x000008/* Part of FLASHA. CSM password locations in FLASHA */

IQTABLES: origin = 0x3FE000, length = 0x000B50/* IQ Math Tables in Boot ROM */

IQTABLES2: origin = 0x3FEB50, length = 0x00008C/* IQ Math Tables in Boot ROM */

IQTABLES3: origin = 0x3FEBDC, length = 0x0000AA/* IQ Math Tables in Boot ROM */

BOOTROM: origin = 0x3FF27C, length = 0x000D44/* Boot ROM */

RESET: origin = 0x3FFFC0, length = 0x000002/* part of boot ROM */

VECTORS: origin = 0x3FFFC2, length = 0x00003E/* part of boot ROM */

PAGE 1 :

BOOT_RSVD: origin = 0x000000, length = 0x000050/* Part of M0, BOOT rom will use this for stack */

RAMM0: origin = 0x000050, length = 0x0003B0/* on-chip RAM block M0 */ RAMM1: origin = 0x000400, length = 0x00400/* on-chip RAM block M1 */

/* RAMM1a: origin = 0x000400, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1b: origin = 0x000500, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1c: origin = 0x000600, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1d: origin = 0x000700, length = 0x00100*//* on-chip RAM block M1 */

dlog1RAM : origin = 0x009000, length = 0x00200

dlog2RAM : origin = 0x009200, length = 0x00200

dlog3RAM : origin = 0x009400, length = 0x00200

/* dataRAM: origin = 0x009000, length = 0x000F00*//* data RAM (L3) */

dataRAM: origin = 0x009600, length = 0x000900/* data RAM (L3) */

BLDCRAM: origin = 0x009F00, length = 0x000100/* data RAM (L3) */

CLA_CPU_MSGRAM : origin = 0x001480, length = 0x000080 /* CLA-R/W, CPU-R message RAM */

CPU_CLA_MSGRAM : origin = 0x001500, length = 0x000080 /* CPU-R/W, CLA-R message RAM */

}

SECTIONS

{/* Allocate program areas: */.cinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.pinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.text: >> FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0codestart: > BEGINPAGE = 0ramfuncs: LOAD = FLASHD,RUN = progRAM,LOAD_START(_RamfuncsLoadStart),LOAD_END(_RamfuncsLoadEnd),RUN_START(_RamfuncsRunStart),PAGE = 0csmpasswds: > CSM_PWLPAGE = 0csm_rsvd: > CSM_RSVDPAGE = 0/* Allocate uninitalized data sections: */.stack: > RAMM0,PAGE = 1.ebss: > dataRAM,PAGE = 1.esysmem: > dataRAM,PAGE = 1DLOG: > dataRAM,PAGE = 1

/*DLOG1: > RAMM1a,PAGE = 1*/

/*DLOG2: > RAMM1b,PAGE = 1*/

/*DLOG3: > RAMM1c,PAGE = 1*/

/*DLOG4: > RAMM1d,PAGE = 1*/DLOG1: > dlog1RAM,PAGE = 1DLOG2: > dlog2RAM,PAGE = 1DLOG3: > dlog3RAM,PAGE = 1BLDC: > BLDCRAM,PAGE = 1/* Initalized sections go in Flash *//* For SDFlash to program these, they must be allocated to page 0 */.econst: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0.switch: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Allocate IQ math areas: */IQmath: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Math Code */IQmathTables: > IQTABLESPAGE = 0, TYPE = NOLOAD/* Math Tables In ROM */Cla1ToCpuMsgRAM: > CLA_CPU_MSGRAM PAGE = 1CpuToCla1MsgRAM: > CPU_CLA_MSGRAM PAGE = 1.reset: > RESET,PAGE = 0, TYPE = DSECTvectors: > VECTORSPAGE = 0, TYPE = DSECT/* Uncomment the section below if calling the IQNexp() or IQexp()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables2: > IQTABLES2, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)}*//* Uncomment the section below if calling the IQNasin() or IQasin()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables3: > IQTABLES3, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)}*/

}

编译有一个warning,

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQ24div.obj>":

compatibility cannot be determined

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQmathTables.obj>":

compatibility cannot be determined

说是编译器版本问题。

现在能顺利下载,功能正常,但是断电重启后程序不运行,请问如何解决????

ruitian fan:

回复 囧:

bootmode应该没问题,因为gui工程已经测试过了,再没对硬件任何更改的情况下,gui工程断电再上电是可以运行的,是可以保存程序的

TI官方开发板: DRV8301-HC-C2-KIT,控制卡dsp是F28035,电机驱动芯片是DRV8301,导入controlsuit默认的示例工程

InstaSPIN-BLDC和InstaSPIN_BLDC。

GUI工程默认就是从flash启动,而instaSPIN-BLDC工程默认从ram启动,现在需要instaSPIN-BLDC工程也需要从flash启动,对instaSPIN-BLDC工程做了几处更改:

1.增加2个按键中断,中断函数名称

void xint1_isr(void);

void xint2_isr(void);

2.在dac中断里面读取了电位器dac的数值,并且进行了简单的赋值操作

现在在ram中运行良好,没什么异常。

参照GUI工程从flash启动,首先在工程里面定义编译宏FLASH,将自带的cmd文件用gui中的cmd文件覆盖,并且对工程进行了修改,

修改的主要位置为:

BLDC_Int.c中

#ifdef FLASH #pragma CODE_SECTION(MainISR,"ramfuncs"); #pragma CODE_SECTION(xint1_isr,"ramfuncs"); #pragma CODE_SECTION(xint2_isr,"ramfuncs"); #pragma DATA_SECTION(InstaSPIN_BLDC1,"BLDC"); void MemCopy(); void InitFlash(); #endif

对cmd文件也进行了修改,修改后的cmd文件为:

/*==================================================================================*/

/* User specific Linker command file for running from FLASH */

/*==================================================================================*/

/* FILE: F28035_FLASH_DRV8412GUI.CMD*/

/**/

/* Description: Linker command file for User custom sections targetted to run*/

/* from FLASH.*/

/**/

/* Target: TMS320F28035*/

/**/

/* Version: 1.00 */

/**/

/*----------------------------------------------------------------------------------*/

/* Copyright Texas Instruments �2009*/

/*----------------------------------------------------------------------------------*/

/* Revision History:*/

/*----------------------------------------------------------------------------------*/

/* Date| Description*/

/*----------------------------------------------------------------------------------*/

/* 4/13/09 | Release 1.0 New release.*/

/*----------------------------------------------------------------------------------*/

/* Define the memory block start/length for the F28035PAGE 0 will be used to organize program sectionsPAGE 1 will be used to organize data sectionsNotes:Memory blocks on F2803x are uniform (ie samephysical memory) in both PAGE 0 and PAGE 1.That is the same memory region should not bedefined for both PAGE 0 and PAGE 1.Doing so will result in corruption of programand/or data.L0 memory block is mirrored - that isit can be accessed in high memory or low memory.For simplicity only one instance is used in thislinker file.Contiguous SARAM memory blocks or flash sectors can bebe combined if required to create a larger memory block.

*/

MEMORY

{

/* Note that the memory allocation below does not create sections as necessary forthe CLA on the F2803x.

*/

PAGE 0:

progRAM: origin = 0x008000, length = 0x001000 /* on-chip RAM (L0-L2)*/

OTP: origin = 0x3D7800, length = 0x000400/* on-chip OTP */

FLASHH: origin = 0x3E8000, length = 0x002000/* on-chip FLASH */

FLASHG: origin = 0x3EA000, length = 0x002000/* on-chip FLASH */

FLASHF: origin = 0x3EC000, length = 0x002000/* on-chip FLASH */

FLASHE: origin = 0x3EE000, length = 0x002000/* on-chip FLASH */

FLASHD: origin = 0x3F0000, length = 0x002000/* on-chip FLASH */

FLASHC: origin = 0x3F2000, length = 0x002000/* on-chip FLASH */

FLASHB: origin = 0x3F4000, length = 0x002000/* on-chip FLASH */

FLASHA: origin = 0x3F6000, length = 0x001F80/* on-chip FLASH */

CSM_RSVD: origin = 0x3F7F80, length = 0x000076/* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN: origin = 0x3F7FF6, length = 0x000002/* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL: origin = 0x3F7FF8, length = 0x000008/* Part of FLASHA. CSM password locations in FLASHA */

IQTABLES: origin = 0x3FE000, length = 0x000B50/* IQ Math Tables in Boot ROM */

IQTABLES2: origin = 0x3FEB50, length = 0x00008C/* IQ Math Tables in Boot ROM */

IQTABLES3: origin = 0x3FEBDC, length = 0x0000AA/* IQ Math Tables in Boot ROM */

BOOTROM: origin = 0x3FF27C, length = 0x000D44/* Boot ROM */

RESET: origin = 0x3FFFC0, length = 0x000002/* part of boot ROM */

VECTORS: origin = 0x3FFFC2, length = 0x00003E/* part of boot ROM */

PAGE 1 :

BOOT_RSVD: origin = 0x000000, length = 0x000050/* Part of M0, BOOT rom will use this for stack */

RAMM0: origin = 0x000050, length = 0x0003B0/* on-chip RAM block M0 */ RAMM1: origin = 0x000400, length = 0x00400/* on-chip RAM block M1 */

/* RAMM1a: origin = 0x000400, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1b: origin = 0x000500, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1c: origin = 0x000600, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1d: origin = 0x000700, length = 0x00100*//* on-chip RAM block M1 */

dlog1RAM : origin = 0x009000, length = 0x00200

dlog2RAM : origin = 0x009200, length = 0x00200

dlog3RAM : origin = 0x009400, length = 0x00200

/* dataRAM: origin = 0x009000, length = 0x000F00*//* data RAM (L3) */

dataRAM: origin = 0x009600, length = 0x000900/* data RAM (L3) */

BLDCRAM: origin = 0x009F00, length = 0x000100/* data RAM (L3) */

CLA_CPU_MSGRAM : origin = 0x001480, length = 0x000080 /* CLA-R/W, CPU-R message RAM */

CPU_CLA_MSGRAM : origin = 0x001500, length = 0x000080 /* CPU-R/W, CLA-R message RAM */

}

SECTIONS

{/* Allocate program areas: */.cinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.pinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.text: >> FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0codestart: > BEGINPAGE = 0ramfuncs: LOAD = FLASHD,RUN = progRAM,LOAD_START(_RamfuncsLoadStart),LOAD_END(_RamfuncsLoadEnd),RUN_START(_RamfuncsRunStart),PAGE = 0csmpasswds: > CSM_PWLPAGE = 0csm_rsvd: > CSM_RSVDPAGE = 0/* Allocate uninitalized data sections: */.stack: > RAMM0,PAGE = 1.ebss: > dataRAM,PAGE = 1.esysmem: > dataRAM,PAGE = 1DLOG: > dataRAM,PAGE = 1

/*DLOG1: > RAMM1a,PAGE = 1*/

/*DLOG2: > RAMM1b,PAGE = 1*/

/*DLOG3: > RAMM1c,PAGE = 1*/

/*DLOG4: > RAMM1d,PAGE = 1*/DLOG1: > dlog1RAM,PAGE = 1DLOG2: > dlog2RAM,PAGE = 1DLOG3: > dlog3RAM,PAGE = 1BLDC: > BLDCRAM,PAGE = 1/* Initalized sections go in Flash *//* For SDFlash to program these, they must be allocated to page 0 */.econst: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0.switch: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Allocate IQ math areas: */IQmath: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Math Code */IQmathTables: > IQTABLESPAGE = 0, TYPE = NOLOAD/* Math Tables In ROM */Cla1ToCpuMsgRAM: > CLA_CPU_MSGRAM PAGE = 1CpuToCla1MsgRAM: > CPU_CLA_MSGRAM PAGE = 1.reset: > RESET,PAGE = 0, TYPE = DSECTvectors: > VECTORSPAGE = 0, TYPE = DSECT/* Uncomment the section below if calling the IQNexp() or IQexp()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables2: > IQTABLES2, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)}*//* Uncomment the section below if calling the IQNasin() or IQasin()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables3: > IQTABLES3, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)}*/

}

编译有一个warning,

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQ24div.obj>":

compatibility cannot be determined

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQmathTables.obj>":

compatibility cannot be determined

说是编译器版本问题。

现在能顺利下载,功能正常,但是断电重启后程序不运行,请问如何解决????

ruitian fan:

回复 囧:

已经确认了,现在就是11,从FLASH启动。

TI官方开发板: DRV8301-HC-C2-KIT,控制卡dsp是F28035,电机驱动芯片是DRV8301,导入controlsuit默认的示例工程

InstaSPIN-BLDC和InstaSPIN_BLDC。

GUI工程默认就是从flash启动,而instaSPIN-BLDC工程默认从ram启动,现在需要instaSPIN-BLDC工程也需要从flash启动,对instaSPIN-BLDC工程做了几处更改:

1.增加2个按键中断,中断函数名称

void xint1_isr(void);

void xint2_isr(void);

2.在dac中断里面读取了电位器dac的数值,并且进行了简单的赋值操作

现在在ram中运行良好,没什么异常。

参照GUI工程从flash启动,首先在工程里面定义编译宏FLASH,将自带的cmd文件用gui中的cmd文件覆盖,并且对工程进行了修改,

修改的主要位置为:

BLDC_Int.c中

#ifdef FLASH #pragma CODE_SECTION(MainISR,"ramfuncs"); #pragma CODE_SECTION(xint1_isr,"ramfuncs"); #pragma CODE_SECTION(xint2_isr,"ramfuncs"); #pragma DATA_SECTION(InstaSPIN_BLDC1,"BLDC"); void MemCopy(); void InitFlash(); #endif

对cmd文件也进行了修改,修改后的cmd文件为:

/*==================================================================================*/

/* User specific Linker command file for running from FLASH */

/*==================================================================================*/

/* FILE: F28035_FLASH_DRV8412GUI.CMD*/

/**/

/* Description: Linker command file for User custom sections targetted to run*/

/* from FLASH.*/

/**/

/* Target: TMS320F28035*/

/**/

/* Version: 1.00 */

/**/

/*----------------------------------------------------------------------------------*/

/* Copyright Texas Instruments �2009*/

/*----------------------------------------------------------------------------------*/

/* Revision History:*/

/*----------------------------------------------------------------------------------*/

/* Date| Description*/

/*----------------------------------------------------------------------------------*/

/* 4/13/09 | Release 1.0 New release.*/

/*----------------------------------------------------------------------------------*/

/* Define the memory block start/length for the F28035PAGE 0 will be used to organize program sectionsPAGE 1 will be used to organize data sectionsNotes:Memory blocks on F2803x are uniform (ie samephysical memory) in both PAGE 0 and PAGE 1.That is the same memory region should not bedefined for both PAGE 0 and PAGE 1.Doing so will result in corruption of programand/or data.L0 memory block is mirrored - that isit can be accessed in high memory or low memory.For simplicity only one instance is used in thislinker file.Contiguous SARAM memory blocks or flash sectors can bebe combined if required to create a larger memory block.

*/

MEMORY

{

/* Note that the memory allocation below does not create sections as necessary forthe CLA on the F2803x.

*/

PAGE 0:

progRAM: origin = 0x008000, length = 0x001000 /* on-chip RAM (L0-L2)*/

OTP: origin = 0x3D7800, length = 0x000400/* on-chip OTP */

FLASHH: origin = 0x3E8000, length = 0x002000/* on-chip FLASH */

FLASHG: origin = 0x3EA000, length = 0x002000/* on-chip FLASH */

FLASHF: origin = 0x3EC000, length = 0x002000/* on-chip FLASH */

FLASHE: origin = 0x3EE000, length = 0x002000/* on-chip FLASH */

FLASHD: origin = 0x3F0000, length = 0x002000/* on-chip FLASH */

FLASHC: origin = 0x3F2000, length = 0x002000/* on-chip FLASH */

FLASHB: origin = 0x3F4000, length = 0x002000/* on-chip FLASH */

FLASHA: origin = 0x3F6000, length = 0x001F80/* on-chip FLASH */

CSM_RSVD: origin = 0x3F7F80, length = 0x000076/* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN: origin = 0x3F7FF6, length = 0x000002/* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL: origin = 0x3F7FF8, length = 0x000008/* Part of FLASHA. CSM password locations in FLASHA */

IQTABLES: origin = 0x3FE000, length = 0x000B50/* IQ Math Tables in Boot ROM */

IQTABLES2: origin = 0x3FEB50, length = 0x00008C/* IQ Math Tables in Boot ROM */

IQTABLES3: origin = 0x3FEBDC, length = 0x0000AA/* IQ Math Tables in Boot ROM */

BOOTROM: origin = 0x3FF27C, length = 0x000D44/* Boot ROM */

RESET: origin = 0x3FFFC0, length = 0x000002/* part of boot ROM */

VECTORS: origin = 0x3FFFC2, length = 0x00003E/* part of boot ROM */

PAGE 1 :

BOOT_RSVD: origin = 0x000000, length = 0x000050/* Part of M0, BOOT rom will use this for stack */

RAMM0: origin = 0x000050, length = 0x0003B0/* on-chip RAM block M0 */ RAMM1: origin = 0x000400, length = 0x00400/* on-chip RAM block M1 */

/* RAMM1a: origin = 0x000400, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1b: origin = 0x000500, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1c: origin = 0x000600, length = 0x00100*//* on-chip RAM block M1 */

/* RAMM1d: origin = 0x000700, length = 0x00100*//* on-chip RAM block M1 */

dlog1RAM : origin = 0x009000, length = 0x00200

dlog2RAM : origin = 0x009200, length = 0x00200

dlog3RAM : origin = 0x009400, length = 0x00200

/* dataRAM: origin = 0x009000, length = 0x000F00*//* data RAM (L3) */

dataRAM: origin = 0x009600, length = 0x000900/* data RAM (L3) */

BLDCRAM: origin = 0x009F00, length = 0x000100/* data RAM (L3) */

CLA_CPU_MSGRAM : origin = 0x001480, length = 0x000080 /* CLA-R/W, CPU-R message RAM */

CPU_CLA_MSGRAM : origin = 0x001500, length = 0x000080 /* CPU-R/W, CLA-R message RAM */

}

SECTIONS

{/* Allocate program areas: */.cinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.pinit: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0.text: >> FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHH,PAGE = 0codestart: > BEGINPAGE = 0ramfuncs: LOAD = FLASHD,RUN = progRAM,LOAD_START(_RamfuncsLoadStart),LOAD_END(_RamfuncsLoadEnd),RUN_START(_RamfuncsRunStart),PAGE = 0csmpasswds: > CSM_PWLPAGE = 0csm_rsvd: > CSM_RSVDPAGE = 0/* Allocate uninitalized data sections: */.stack: > RAMM0,PAGE = 1.ebss: > dataRAM,PAGE = 1.esysmem: > dataRAM,PAGE = 1DLOG: > dataRAM,PAGE = 1

/*DLOG1: > RAMM1a,PAGE = 1*/

/*DLOG2: > RAMM1b,PAGE = 1*/

/*DLOG3: > RAMM1c,PAGE = 1*/

/*DLOG4: > RAMM1d,PAGE = 1*/DLOG1: > dlog1RAM,PAGE = 1DLOG2: > dlog2RAM,PAGE = 1DLOG3: > dlog3RAM,PAGE = 1BLDC: > BLDCRAM,PAGE = 1/* Initalized sections go in Flash *//* For SDFlash to program these, they must be allocated to page 0 */.econst: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0.switch: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Allocate IQ math areas: */IQmath: > FLASHA|FLASHB|FLASHC|FLASHE|FLASHF|FLASHG|FLASHHPAGE = 0/* Math Code */IQmathTables: > IQTABLESPAGE = 0, TYPE = NOLOAD/* Math Tables In ROM */Cla1ToCpuMsgRAM: > CLA_CPU_MSGRAM PAGE = 1CpuToCla1MsgRAM: > CPU_CLA_MSGRAM PAGE = 1.reset: > RESET,PAGE = 0, TYPE = DSECTvectors: > VECTORSPAGE = 0, TYPE = DSECT/* Uncomment the section below if calling the IQNexp() or IQexp()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables2: > IQTABLES2, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)}*//* Uncomment the section below if calling the IQNasin() or IQasin()functions from the IQMath.lib library in order to utilize therelevant IQ Math table in Boot ROM (This saves space and Boot ROMis 1 wait-state). If this section is not uncommented, IQmathTables2will be loaded into other memory (SARAM, Flash, etc.) and will takeup space, but 0 wait-state is possible.*//*IQmathTables3: > IQTABLES3, PAGE = 0, TYPE = NOLOAD{IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)}*/

}

编译有一个warning,

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQ24div.obj>":

compatibility cannot be determined

warning: build attribute vendor section TI missing in

"C:/TI/controlSUITE/libs/math/IQmath/v15c/lib/IQmath.lib<IQmathTables.obj>":

compatibility cannot be determined

说是编译器版本问题。

现在能顺利下载,功能正常,但是断电重启后程序不运行,请问如何解决????

fei long:

回复 ruitian fan:

请问楼主这个问题解决了吗? 不知道你是怎么解决的

TI中文支持网

TI中文支持网