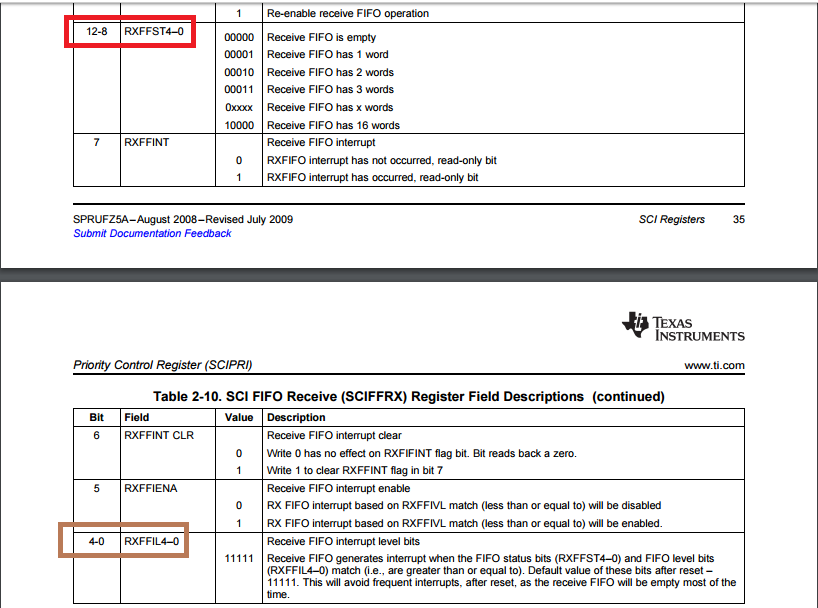

上图为串口接收FIFO寄存器定义

对于FIFO出发中断的条件,适当状态寄存器与设置的fifo深度相等时出发中断。

那么,如果串口接收使用8级FIFO缓存,给串口发送一条3字节的指令,是不是处理器不会响应中断。

若如此,对于不是持续数据流的数据如何使用FIFO缓存避免数据丢失呢

如上所述,接收使用8级FIFO深度。但是指令可能是1个字节、5个字节、4个字节,控制是要对每条指令都要做响应的,但是FIFO中小于8字节不会触发中断,这样不就会造成没有办法正确处理指令长度不能被8整除的指令了吗?

吟啸徐行:其实FIFO一般用来传输固定帧长的协议,如果确实要做非定长的话,可以检查RXWAKE位,当该位为1且接收FIFO有数据,就表示一桢数据已传完。把FIFO中数据取出即可。主要就是RXWAKE不支持中断,所以要高速查询该位的状态,也挺麻烦的。

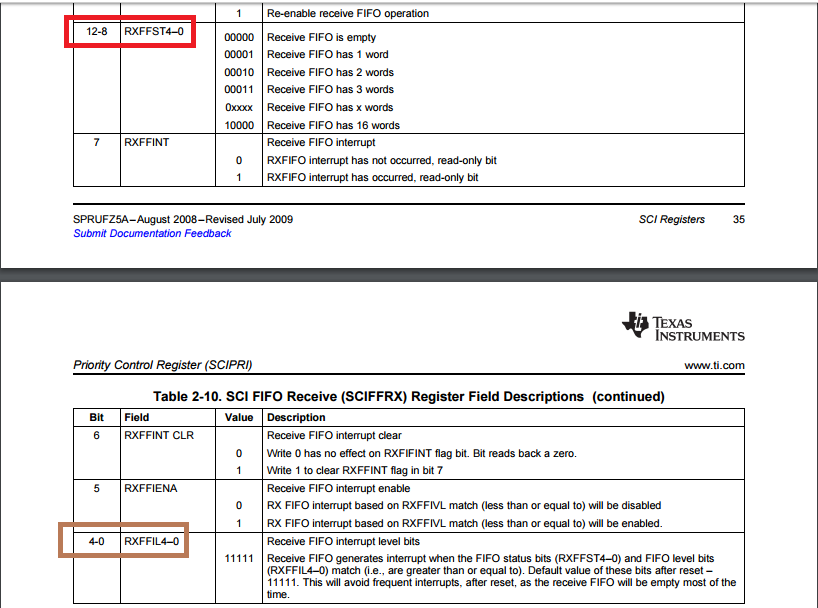

上图为串口接收FIFO寄存器定义

对于FIFO出发中断的条件,适当状态寄存器与设置的fifo深度相等时出发中断。

那么,如果串口接收使用8级FIFO缓存,给串口发送一条3字节的指令,是不是处理器不会响应中断。

若如此,对于不是持续数据流的数据如何使用FIFO缓存避免数据丢失呢

如上所述,接收使用8级FIFO深度。但是指令可能是1个字节、5个字节、4个字节,控制是要对每条指令都要做响应的,但是FIFO中小于8字节不会触发中断,这样不就会造成没有办法正确处理指令长度不能被8整除的指令了吗?

user78960159:

回复 吟啸徐行:

您好 感谢您的帮助 我会贴出我花的一个时许分析图 麻烦有时间帮我看下 多谢

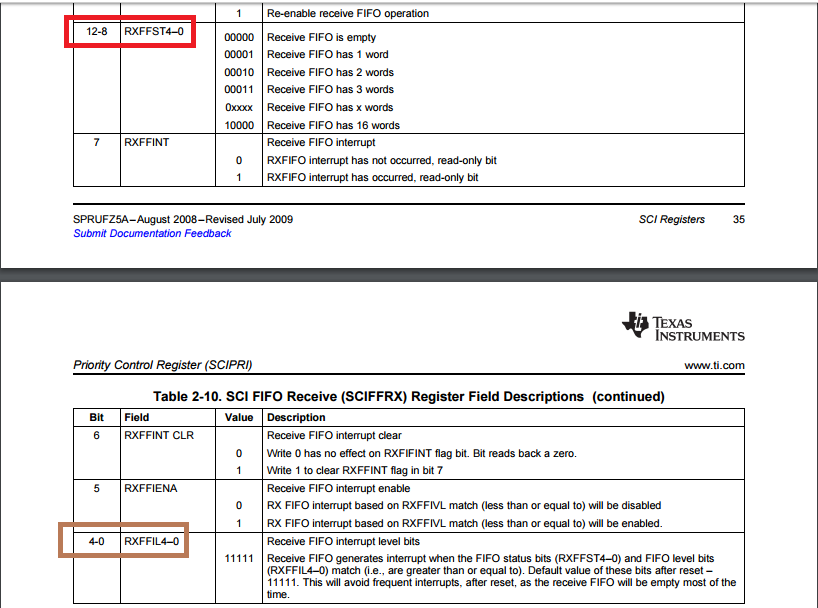

上图为串口接收FIFO寄存器定义

对于FIFO出发中断的条件,适当状态寄存器与设置的fifo深度相等时出发中断。

那么,如果串口接收使用8级FIFO缓存,给串口发送一条3字节的指令,是不是处理器不会响应中断。

若如此,对于不是持续数据流的数据如何使用FIFO缓存避免数据丢失呢

如上所述,接收使用8级FIFO深度。但是指令可能是1个字节、5个字节、4个字节,控制是要对每条指令都要做响应的,但是FIFO中小于8字节不会触发中断,这样不就会造成没有办法正确处理指令长度不能被8整除的指令了吗?

user78960159:

回复 mangui zhang:

您好 感谢您的帮助 我会贴出我花的一个时许分析图 麻烦有时间帮我看下 多谢

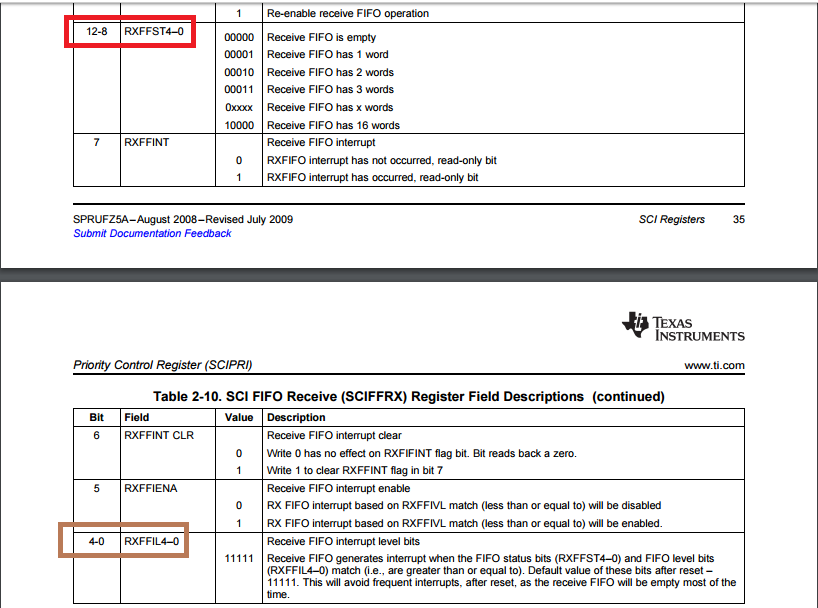

上图为串口接收FIFO寄存器定义

对于FIFO出发中断的条件,适当状态寄存器与设置的fifo深度相等时出发中断。

那么,如果串口接收使用8级FIFO缓存,给串口发送一条3字节的指令,是不是处理器不会响应中断。

若如此,对于不是持续数据流的数据如何使用FIFO缓存避免数据丢失呢

如上所述,接收使用8级FIFO深度。但是指令可能是1个字节、5个字节、4个字节,控制是要对每条指令都要做响应的,但是FIFO中小于8字节不会触发中断,这样不就会造成没有办法正确处理指令长度不能被8整除的指令了吗?

user78960159:

回复 user78960159:

感谢二位的帮助

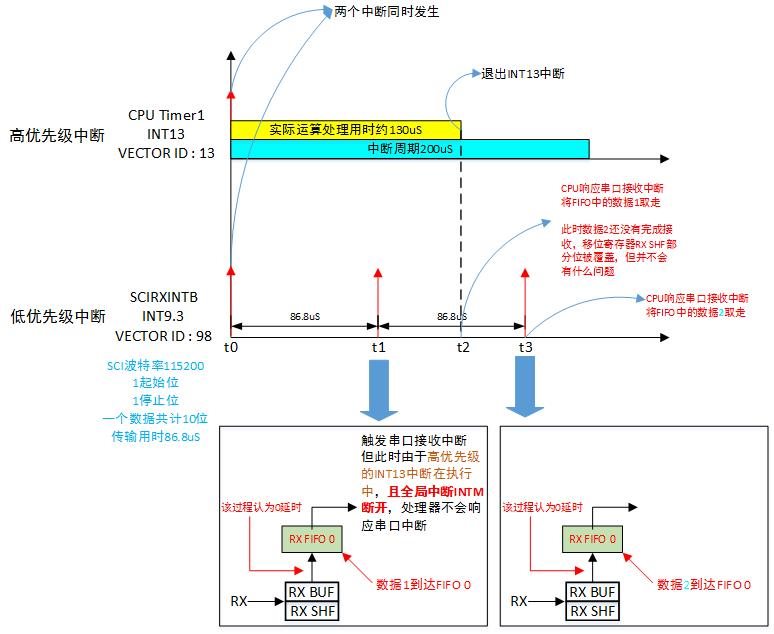

上图为画的一个时许分析图,C2000系列处理器当进入到一个中断函数后会关闭全局中断,且处理器有默认的中断优先级是固定的,实现中断嵌套不是很方便。

不过官方给出了一个例程,大家在用的时候一般是不是还是用的C2000默认的中断机制呢?

若如此,我分析了下我的系统,为的是不丢失串口数据,如上图所示

我的系统里有两个中断,CPU Timer1中断INT13及串口B接收中断,考虑两个中断同时发生的情况,如上图所示。

串口波特率115200,停止位1,不做校验,一个数据10bit

CPU Timer1中断周期为200uS,在其中的算法处理最长时间约130uS,具体分析如上图所示,我分析认为应该不会出现数据丢失的问题,请大家帮我确认下,谢谢!

在这个情况下,加1级FIFO与不加FIFO是不是同样都不会丢失数据呢?

TI中文支持网

TI中文支持网