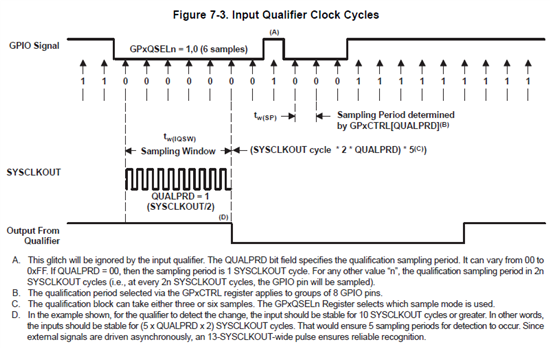

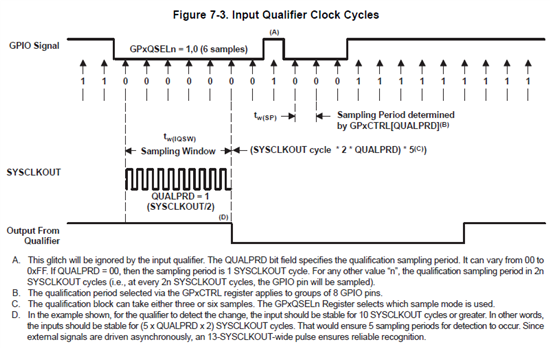

本人正研究关于28377D输入GPIO管脚针对输入的脉冲信号需要多宽才能有效捕获的问题,看了两个寄存器,分别为GPXCTRL和GPXQSELn;

按照我的理解,如下图所示:

按理说只要配置好对应管脚上述两个寄存器的数值即可以实现关于脉冲宽度限制的问题;

比如在运行的过程中运行如下语句(期间令KKK=1一次)

if(KKK==1)

{

KKK=0;

EALLOW;

GpioCtrlRegs.GPBCTRL.bit.QUALPRD0=100;//作为输入管脚,每个采样周期中的时钟周期为100*2个SYSCLK=1us,SYSCLK=200MHz

GpioCtrlRegs.GPBQSEL1.bit.GPIO34=2;//作为输入管脚,采样周期为6个上述时钟周期,即6*1us=6us;

EDIS;

}

在没有设置GPXLOCK寄存器和GPXCR寄存器的情况下运行上面代码,也就是调整到采样宽度达到6us,但不理解的是在该管脚的500ns正脉冲总是可以触发配置好的EINT1(正边沿触发);

想要确认测试这个输入管脚的有效脉宽问题,是不是可以如我上述处理,还是哪里理解错误了???

GpioCtrlRegs.GPBCR.bit.GPIO34=0;

GpioCtrlRegs.GPBLOCK.bit.GPIO34=0;

但现象上看

Eric Ma:

我看了文档,你理解的输入滤波功能是合理的。

如例程设置也是很简单配置两行寄存器

C:\ti\controlSUITE\device_support\F2837xS\v210\F2837xS_examples_Cpu1\gpio_setup\cpu01

你可以试试在初始化一开始的时候,就直接配置这个滤波功能。

本人正研究关于28377D输入GPIO管脚针对输入的脉冲信号需要多宽才能有效捕获的问题,看了两个寄存器,分别为GPXCTRL和GPXQSELn;

按照我的理解,如下图所示:

按理说只要配置好对应管脚上述两个寄存器的数值即可以实现关于脉冲宽度限制的问题;

比如在运行的过程中运行如下语句(期间令KKK=1一次)

if(KKK==1)

{

KKK=0;

EALLOW;

GpioCtrlRegs.GPBCTRL.bit.QUALPRD0=100;//作为输入管脚,每个采样周期中的时钟周期为100*2个SYSCLK=1us,SYSCLK=200MHz

GpioCtrlRegs.GPBQSEL1.bit.GPIO34=2;//作为输入管脚,采样周期为6个上述时钟周期,即6*1us=6us;

EDIS;

}

在没有设置GPXLOCK寄存器和GPXCR寄存器的情况下运行上面代码,也就是调整到采样宽度达到6us,但不理解的是在该管脚的500ns正脉冲总是可以触发配置好的EINT1(正边沿触发);

想要确认测试这个输入管脚的有效脉宽问题,是不是可以如我上述处理,还是哪里理解错误了???

GpioCtrlRegs.GPBCR.bit.GPIO34=0;

GpioCtrlRegs.GPBLOCK.bit.GPIO34=0;

但现象上看

mangui zhang:

除了多宽才能捕获到外 还要主函数中一直干这事去

其他的都不干

TI中文支持网

TI中文支持网