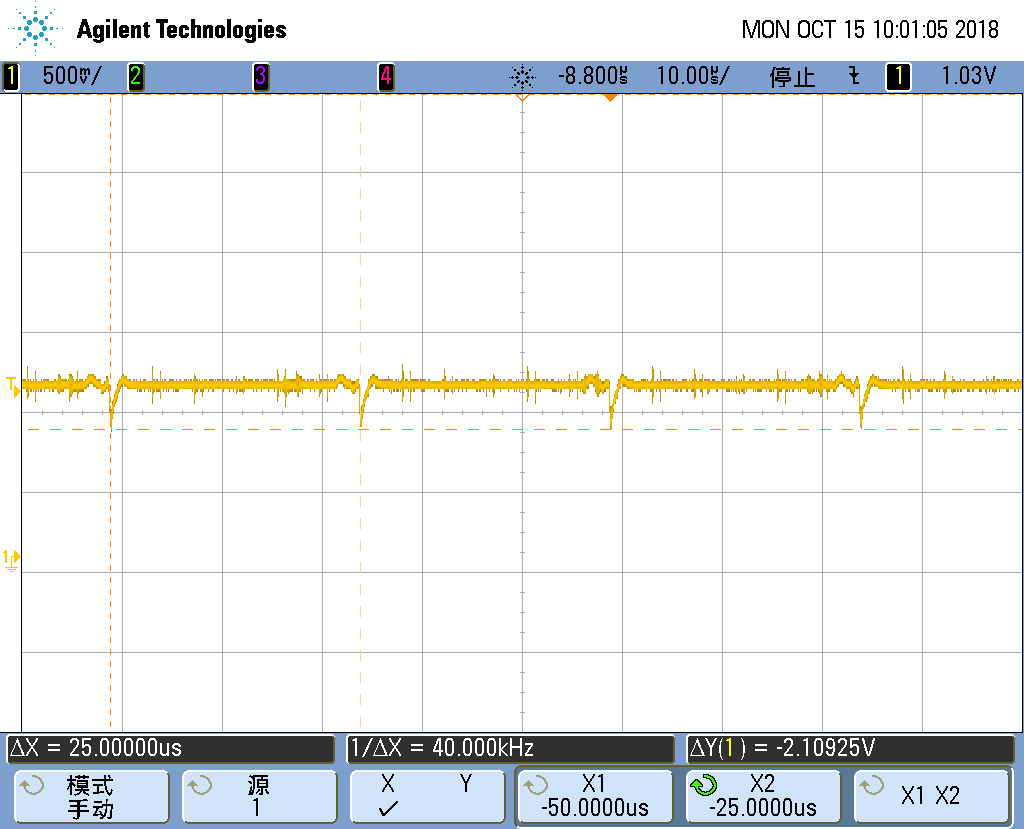

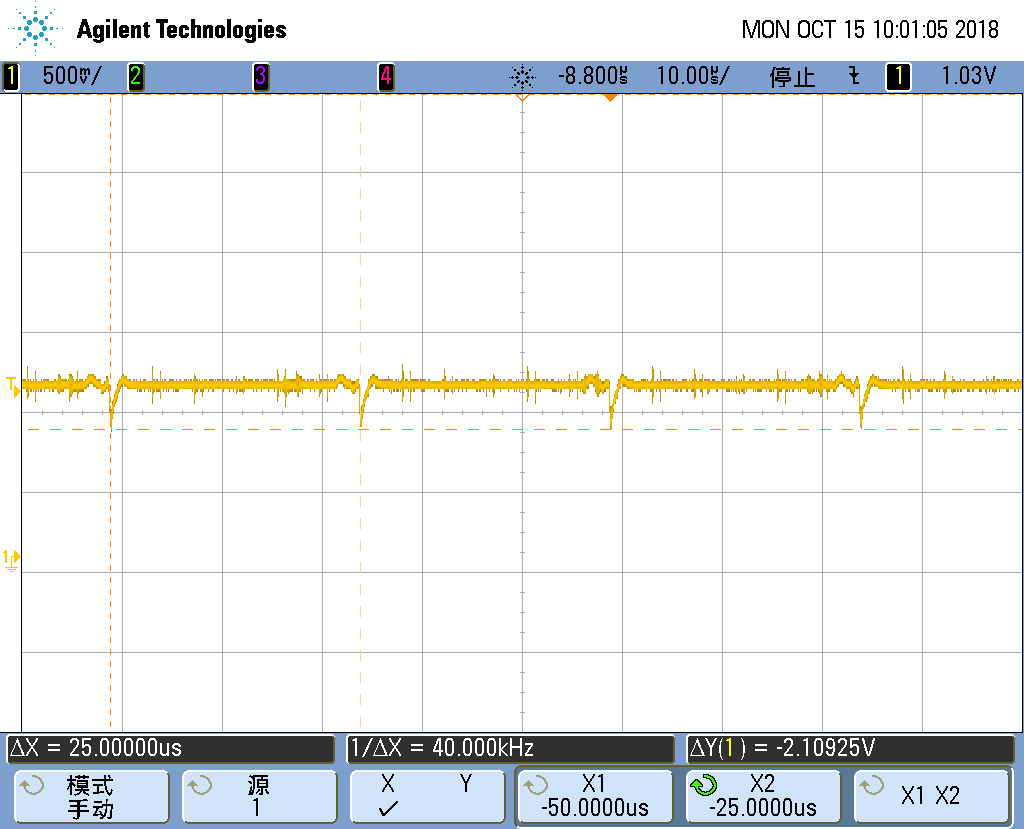

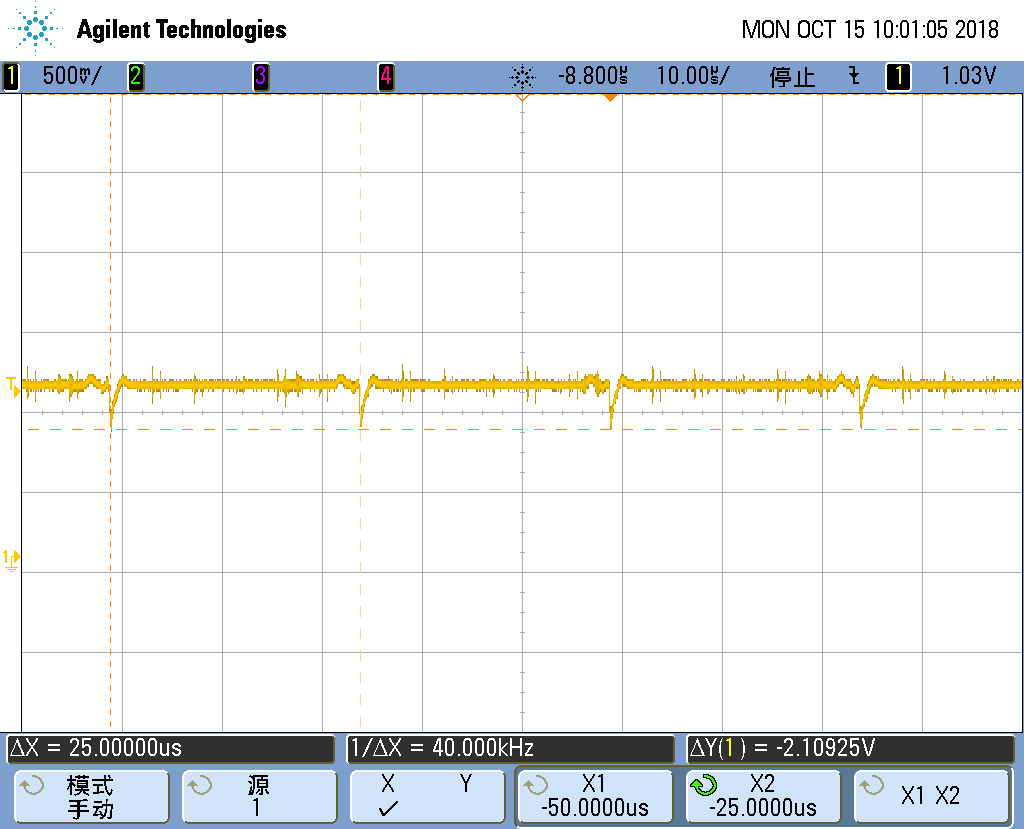

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

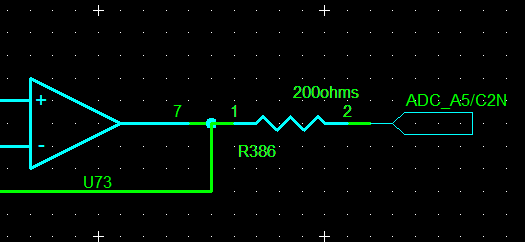

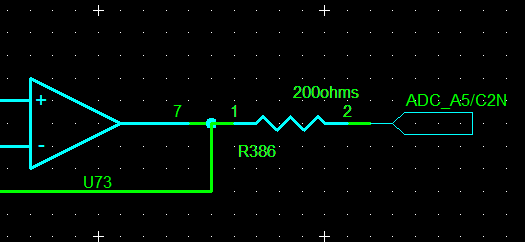

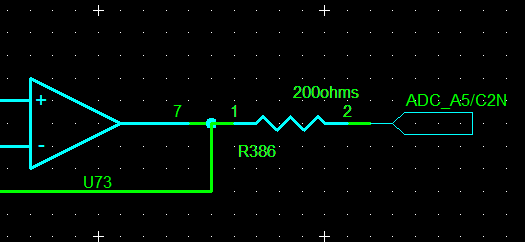

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

Howard Zou:ACQPS是多少,尝试增大采样窗看看是否有改进。

另外你这个现象和ADC通道有关系吗?是否每个ADC通道都是这样?

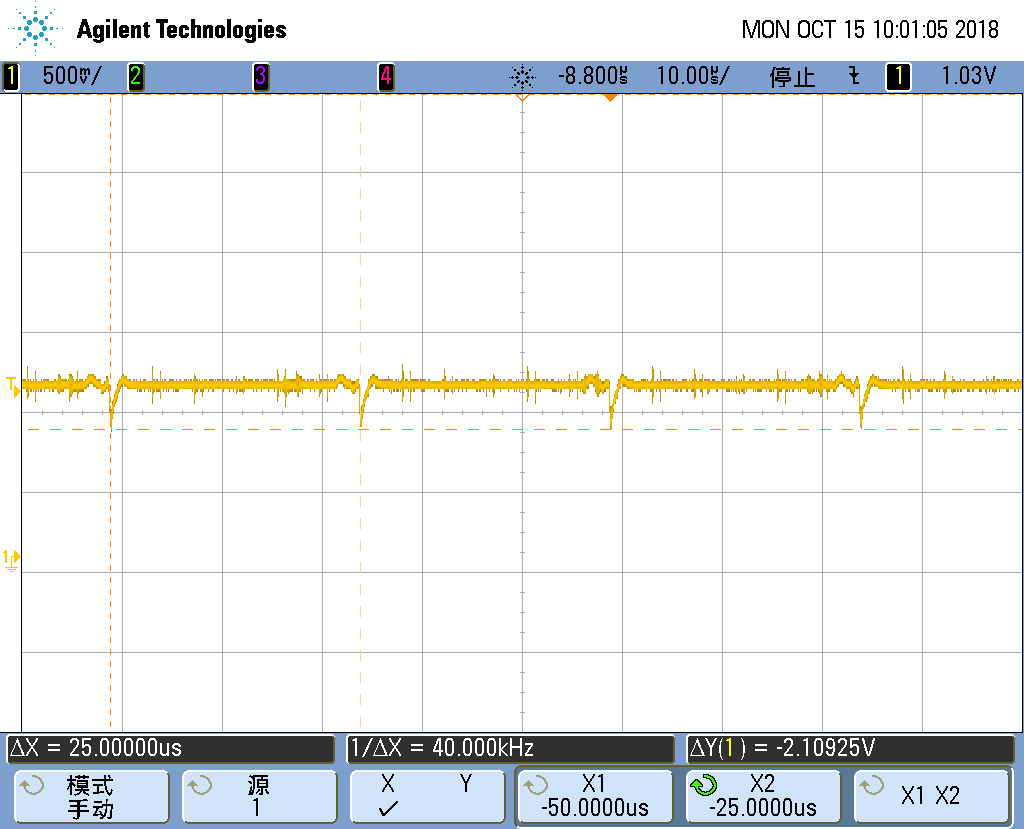

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

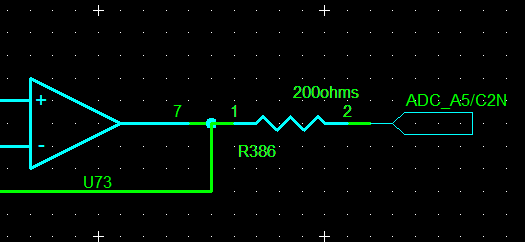

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

user4373386:

回复 Howard Zou:

目前该现象和ADC通道是有关系的,28075的17路AD采样我全用完了,出现该现象的引脚是ADCA5引脚和ADC15引脚。前两天我拿ADC的A模块去触发ADC15引脚采样时,会出现这个现象,但是改成拿ADC的B模块或D模块去触发ADC15引脚采样,则不会出现这个现象。然而我看28075的数据手册的描述是ADC15引脚被ADC的A模块或B模块或D模块触发采样都是允许的。然后今天我拿ADCA5引脚采样,也发现了该现象,然而ADCA5只能被ADC的A模块触发,所以没进行后续验证了。其余15个采样引脚目前没发现这个现象。目前所有采样通道的采样窗口时间都是200ns,我尝试过增大采样窗口,但是现象是一样的。

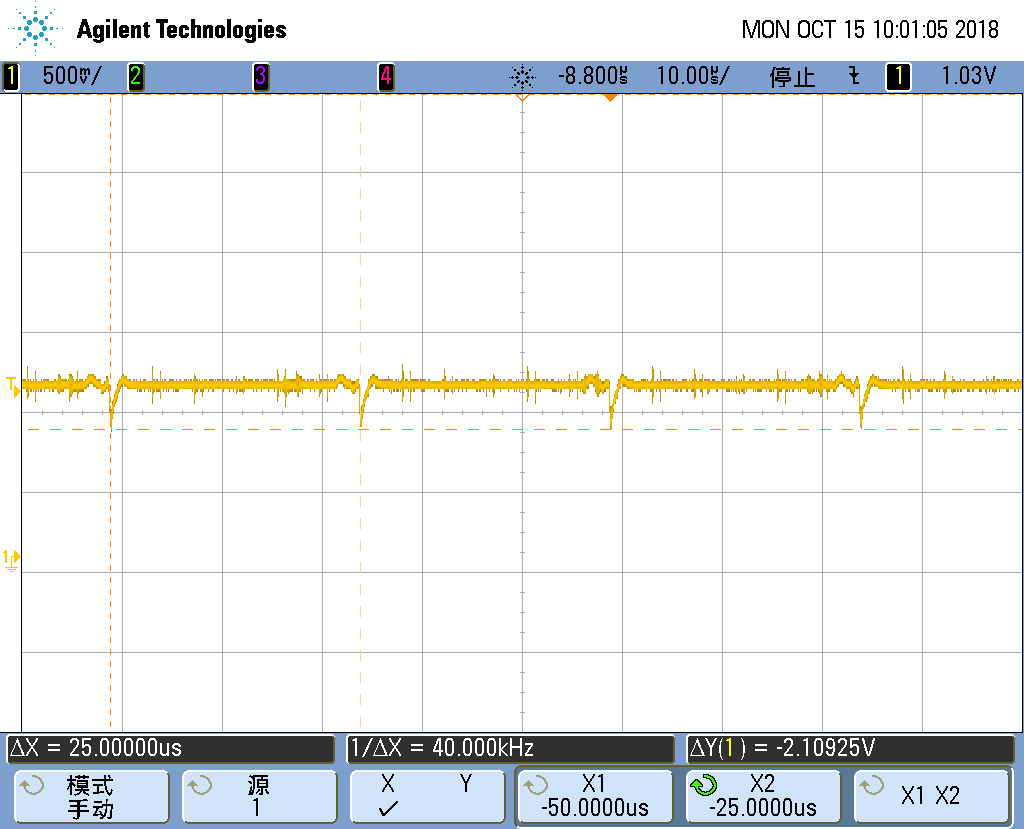

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

Howard Zou:

回复 user4373386:

ADC15是哪个引脚?我看不到。

另外你说“我拿ADC的A模块去触发ADC15引脚采样时”,这句话是什么意思?你的触发源是什么?

200Ohm后面没有对地电容吗?

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

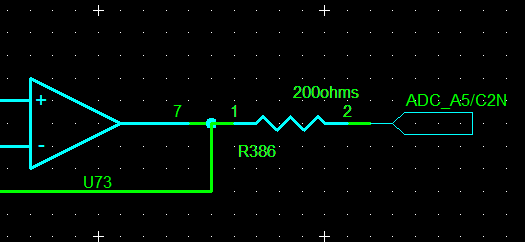

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

user4373386:

回复 Howard Zou:

这个问题现在解决了,发现是因为有一路ADC采样引脚给了个负电平导致的。后来把该负电平去掉就没问题了。

ADC15引脚是ADCIN15引脚。

“我拿ADC的A模块去触发ADC15引脚采样时”,这句话意思是拿ADC的A模块去触发ADC15引脚的采样。因为ADC15引脚允许被A、B或D模块的SOC触发采样。

200欧后面有对地电容

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

JLDN:

回复 user4373386:

你好!请问发现是因为有一路ADC采样引脚给了个负电平导致的。后来把该负电平去掉就没问题了。这个负电平是指电压在0V的时候运放的偏移导致的很小的负电压?请问你是如何把这个负电压去掉的?

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?

user450161651:

回复 JLDN:

负电平是怎么给的?

TI中文支持网

TI中文支持网