28377D使用emif对FPGA进行读写(16-bit,异步模式)的时候,不输出正确的地址,没有拉低CS2,RNW和WE信号都不正确。已经遵循手册,用EMxBA1取代A0,然后将[A7:A1]连接到[A6:A0]。下面附上了代码和截图,求一些思路。

#include "F28x_Project.h"

void main(void)

{

InitSysCtrl();

EALLOW;

ClkCfgRegs.PERCLKDIVSEL.bit.EMIF1CLKDIV = 1; // PLLSYSCLK 1/2 for EMIF

EDIS;

InitGpio();

EALLOW;

//led

GpioCtrlRegs.GPEMUX1.bit.GPIO133=0;

GpioCtrlRegs.GPEDIR.bit.GPIO133=1;

//cs2 rd we

GpioCtrlRegs.GPBMUX1.bit.GPIO32=2; //cs0 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO34=2; //cs2 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO33=2; //RNW HIGH ENABLE

GpioCtrlRegs.GPAMUX2.bit.GPIO31=2; //WE LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO37=2; //EM1OE LOW ENABLE

//addr

GpioCtrlRegs.GPCMUX2.bit.GPIO92=3; //EM1BA1

GpioCtrlRegs.GPBMUX1.bit.GPIO38=2; //A0

GpioCtrlRegs.GPBMUX1.bit.GPIO39=2; //A1

GpioCtrlRegs.GPBMUX1.bit.GPIO40=2; //A2

GpioCtrlRegs.GPBMUX1.bit.GPIO41=2; //A3

GpioCtrlRegs.GPBMUX1.bit.GPIO44=2; //A4

GpioCtrlRegs.GPBMUX1.bit.GPIO45=2; //A5

GpioCtrlRegs.GPBMUX1.bit.GPIO46=2; //A6

GpioCtrlRegs.GPBMUX1.bit.GPIO47=2; //A7

GpioCtrlRegs.GPBMUX2.bit.GPIO48=2; //A8

GpioCtrlRegs.GPBMUX2.bit.GPIO49=2; //A9

GpioCtrlRegs.GPBMUX2.bit.GPIO50=2; //A10

GpioCtrlRegs.GPBMUX2.bit.GPIO51=2; //A11

GpioCtrlRegs.GPBMUX2.bit.GPIO52=2; //A12

GpioCtrlRegs.GPCMUX2.bit.GPIO86=2; //A13

GpioCtrlRegs.GPCMUX2.bit.GPIO87=2; //A14

GpioCtrlRegs.GPCMUX2.bit.GPIO88=2; //A15

GpioCtrlRegs.GPCMUX2.bit.GPIO89=2; //A16

GpioCtrlRegs.GPCMUX2.bit.GPIO90=2; //A17

GpioCtrlRegs.GPCMUX2.bit.GPIO91=2; //A18

//GpioCtrlRegs.GPCMUX2.bit.GPIO92=2; //A19

//data

GpioCtrlRegs.GPCMUX1.bit.GPIO69=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO70=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO71=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO72=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO73=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO74=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO75=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO76=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO77=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO78=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO79=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO80=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO81=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO82=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO83=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO85=2;

EDIS;

Emif1Regs.ASYNC_CS2_CR.all = (EMIF_ASYNC_ASIZE_16| //16位内存EMIF_ASYNC_TA_4| //Turn AroundEMIF_ASYNC_RHOLD_8| //读保持时间EMIF_ASYNC_RSTROBE_64 | //读选通 时间EMIF_ASYNC_RSETUP_16| //读建立时间EMIF_ASYNC_WHOLD_8| //写保持时间EMIF_ASYNC_WSTROBE_64 | //写选通时间EMIF_ASYNC_WSETUP_16| //写建立时间EMIF_ASYNC_EW_DISABLE | //拓展等待禁用EMIF_ASYNC_SS_DISABLE); //strobe select模式禁用

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EINT;

int i;

Uint16 *ExRamStart = (Uint16*)0x00100000;for(i=0; i<0x0008; i++) {*(ExRamStart+i)=0x6666; }while(1){

GpioDataRegs.GPECLEAR.bit.GPIO133=1;

DELAY_US (500000);

GpioDataRegs.GPESET.bit.GPIO133=1;

DELAY_US (500000);}

}

Green Deng:你好,我看到你的描述中有提到“没有拉低CS2,RNW和WE信号都不正确”,请问你目前能确保硬件上都运行正常吗?

28377D使用emif对FPGA进行读写(16-bit,异步模式)的时候,不输出正确的地址,没有拉低CS2,RNW和WE信号都不正确。已经遵循手册,用EMxBA1取代A0,然后将[A7:A1]连接到[A6:A0]。下面附上了代码和截图,求一些思路。

#include "F28x_Project.h"

void main(void)

{

InitSysCtrl();

EALLOW;

ClkCfgRegs.PERCLKDIVSEL.bit.EMIF1CLKDIV = 1; // PLLSYSCLK 1/2 for EMIF

EDIS;

InitGpio();

EALLOW;

//led

GpioCtrlRegs.GPEMUX1.bit.GPIO133=0;

GpioCtrlRegs.GPEDIR.bit.GPIO133=1;

//cs2 rd we

GpioCtrlRegs.GPBMUX1.bit.GPIO32=2; //cs0 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO34=2; //cs2 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO33=2; //RNW HIGH ENABLE

GpioCtrlRegs.GPAMUX2.bit.GPIO31=2; //WE LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO37=2; //EM1OE LOW ENABLE

//addr

GpioCtrlRegs.GPCMUX2.bit.GPIO92=3; //EM1BA1

GpioCtrlRegs.GPBMUX1.bit.GPIO38=2; //A0

GpioCtrlRegs.GPBMUX1.bit.GPIO39=2; //A1

GpioCtrlRegs.GPBMUX1.bit.GPIO40=2; //A2

GpioCtrlRegs.GPBMUX1.bit.GPIO41=2; //A3

GpioCtrlRegs.GPBMUX1.bit.GPIO44=2; //A4

GpioCtrlRegs.GPBMUX1.bit.GPIO45=2; //A5

GpioCtrlRegs.GPBMUX1.bit.GPIO46=2; //A6

GpioCtrlRegs.GPBMUX1.bit.GPIO47=2; //A7

GpioCtrlRegs.GPBMUX2.bit.GPIO48=2; //A8

GpioCtrlRegs.GPBMUX2.bit.GPIO49=2; //A9

GpioCtrlRegs.GPBMUX2.bit.GPIO50=2; //A10

GpioCtrlRegs.GPBMUX2.bit.GPIO51=2; //A11

GpioCtrlRegs.GPBMUX2.bit.GPIO52=2; //A12

GpioCtrlRegs.GPCMUX2.bit.GPIO86=2; //A13

GpioCtrlRegs.GPCMUX2.bit.GPIO87=2; //A14

GpioCtrlRegs.GPCMUX2.bit.GPIO88=2; //A15

GpioCtrlRegs.GPCMUX2.bit.GPIO89=2; //A16

GpioCtrlRegs.GPCMUX2.bit.GPIO90=2; //A17

GpioCtrlRegs.GPCMUX2.bit.GPIO91=2; //A18

//GpioCtrlRegs.GPCMUX2.bit.GPIO92=2; //A19

//data

GpioCtrlRegs.GPCMUX1.bit.GPIO69=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO70=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO71=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO72=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO73=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO74=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO75=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO76=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO77=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO78=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO79=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO80=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO81=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO82=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO83=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO85=2;

EDIS;

Emif1Regs.ASYNC_CS2_CR.all = (EMIF_ASYNC_ASIZE_16| //16位内存EMIF_ASYNC_TA_4| //Turn AroundEMIF_ASYNC_RHOLD_8| //读保持时间EMIF_ASYNC_RSTROBE_64 | //读选通 时间EMIF_ASYNC_RSETUP_16| //读建立时间EMIF_ASYNC_WHOLD_8| //写保持时间EMIF_ASYNC_WSTROBE_64 | //写选通时间EMIF_ASYNC_WSETUP_16| //写建立时间EMIF_ASYNC_EW_DISABLE | //拓展等待禁用EMIF_ASYNC_SS_DISABLE); //strobe select模式禁用

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EINT;

int i;

Uint16 *ExRamStart = (Uint16*)0x00100000;for(i=0; i<0x0008; i++) {*(ExRamStart+i)=0x6666; }while(1){

GpioDataRegs.GPECLEAR.bit.GPIO133=1;

DELAY_US (500000);

GpioDataRegs.GPESET.bit.GPIO133=1;

DELAY_US (500000);}

}

2Husky:

回复 Green Deng:

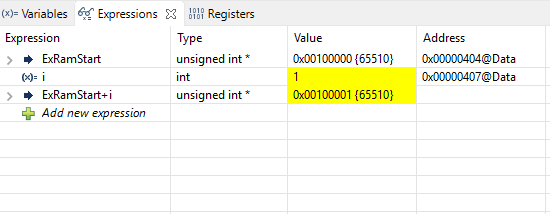

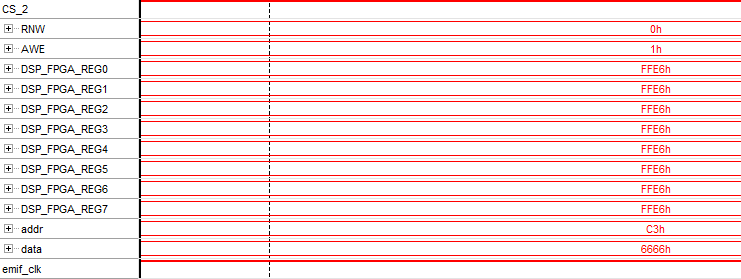

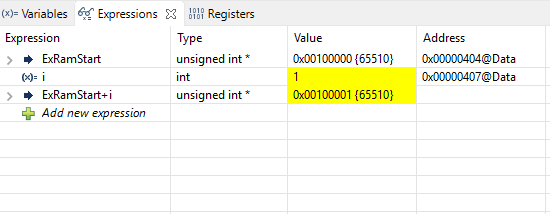

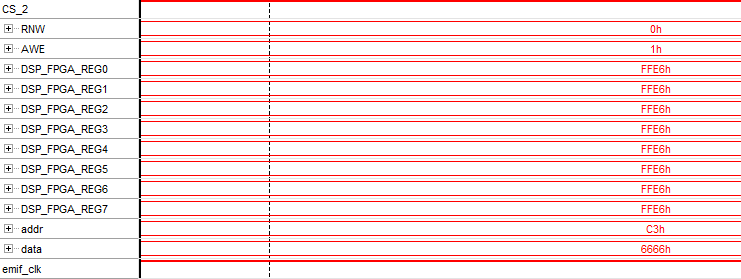

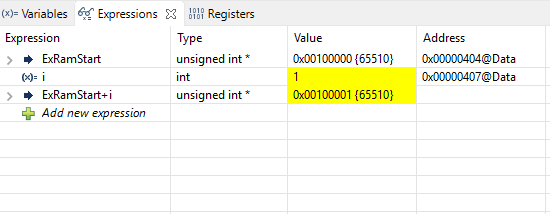

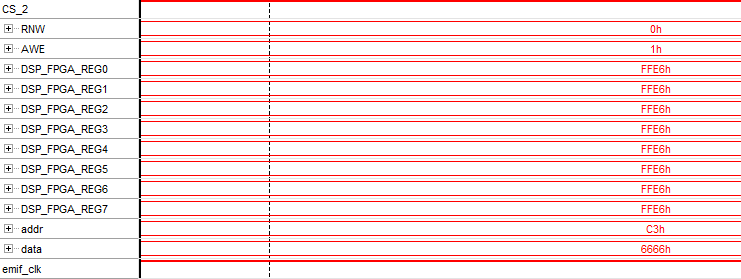

你好,硬件都运行正常。我在GPIO模式下测试过,引脚都是可以拉低的。并且也在加了led观测dsp运行状态。我后来在for循环内进行了单步调试,分别放6663,6666,6669到0000,0001,0002的地址上,发现在循环的时候没有数据放到数据总线上。当结束for循环,进行到while时,最后一个数据,也就是6669h被输出到了数据总线上,此时地址线输出的是C3h。我已经参考了官方例程,不知道是不是还遗漏了什么寄存器。

谢谢

28377D使用emif对FPGA进行读写(16-bit,异步模式)的时候,不输出正确的地址,没有拉低CS2,RNW和WE信号都不正确。已经遵循手册,用EMxBA1取代A0,然后将[A7:A1]连接到[A6:A0]。下面附上了代码和截图,求一些思路。

#include "F28x_Project.h"

void main(void)

{

InitSysCtrl();

EALLOW;

ClkCfgRegs.PERCLKDIVSEL.bit.EMIF1CLKDIV = 1; // PLLSYSCLK 1/2 for EMIF

EDIS;

InitGpio();

EALLOW;

//led

GpioCtrlRegs.GPEMUX1.bit.GPIO133=0;

GpioCtrlRegs.GPEDIR.bit.GPIO133=1;

//cs2 rd we

GpioCtrlRegs.GPBMUX1.bit.GPIO32=2; //cs0 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO34=2; //cs2 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO33=2; //RNW HIGH ENABLE

GpioCtrlRegs.GPAMUX2.bit.GPIO31=2; //WE LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO37=2; //EM1OE LOW ENABLE

//addr

GpioCtrlRegs.GPCMUX2.bit.GPIO92=3; //EM1BA1

GpioCtrlRegs.GPBMUX1.bit.GPIO38=2; //A0

GpioCtrlRegs.GPBMUX1.bit.GPIO39=2; //A1

GpioCtrlRegs.GPBMUX1.bit.GPIO40=2; //A2

GpioCtrlRegs.GPBMUX1.bit.GPIO41=2; //A3

GpioCtrlRegs.GPBMUX1.bit.GPIO44=2; //A4

GpioCtrlRegs.GPBMUX1.bit.GPIO45=2; //A5

GpioCtrlRegs.GPBMUX1.bit.GPIO46=2; //A6

GpioCtrlRegs.GPBMUX1.bit.GPIO47=2; //A7

GpioCtrlRegs.GPBMUX2.bit.GPIO48=2; //A8

GpioCtrlRegs.GPBMUX2.bit.GPIO49=2; //A9

GpioCtrlRegs.GPBMUX2.bit.GPIO50=2; //A10

GpioCtrlRegs.GPBMUX2.bit.GPIO51=2; //A11

GpioCtrlRegs.GPBMUX2.bit.GPIO52=2; //A12

GpioCtrlRegs.GPCMUX2.bit.GPIO86=2; //A13

GpioCtrlRegs.GPCMUX2.bit.GPIO87=2; //A14

GpioCtrlRegs.GPCMUX2.bit.GPIO88=2; //A15

GpioCtrlRegs.GPCMUX2.bit.GPIO89=2; //A16

GpioCtrlRegs.GPCMUX2.bit.GPIO90=2; //A17

GpioCtrlRegs.GPCMUX2.bit.GPIO91=2; //A18

//GpioCtrlRegs.GPCMUX2.bit.GPIO92=2; //A19

//data

GpioCtrlRegs.GPCMUX1.bit.GPIO69=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO70=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO71=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO72=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO73=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO74=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO75=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO76=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO77=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO78=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO79=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO80=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO81=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO82=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO83=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO85=2;

EDIS;

Emif1Regs.ASYNC_CS2_CR.all = (EMIF_ASYNC_ASIZE_16| //16位内存EMIF_ASYNC_TA_4| //Turn AroundEMIF_ASYNC_RHOLD_8| //读保持时间EMIF_ASYNC_RSTROBE_64 | //读选通 时间EMIF_ASYNC_RSETUP_16| //读建立时间EMIF_ASYNC_WHOLD_8| //写保持时间EMIF_ASYNC_WSTROBE_64 | //写选通时间EMIF_ASYNC_WSETUP_16| //写建立时间EMIF_ASYNC_EW_DISABLE | //拓展等待禁用EMIF_ASYNC_SS_DISABLE); //strobe select模式禁用

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EINT;

int i;

Uint16 *ExRamStart = (Uint16*)0x00100000;for(i=0; i<0x0008; i++) {*(ExRamStart+i)=0x6666; }while(1){

GpioDataRegs.GPECLEAR.bit.GPIO133=1;

DELAY_US (500000);

GpioDataRegs.GPESET.bit.GPIO133=1;

DELAY_US (500000);}

}

mangui zhang:

最简单的办法是你在FPGA端进行读写信号监测 然后明白时序关系或判断是否MCU端配置异常

附件为CPLD译码代码 供参考

7585.CPLD.rar

TI中文支持网

TI中文支持网