最近在用28335做电机控制器,遇到了一个比较奇怪的问题。

设计目的:

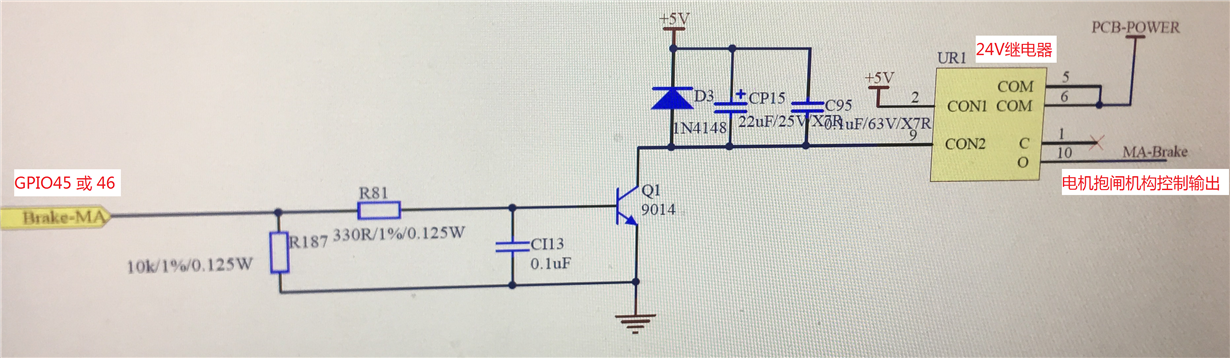

用两个GPIO管脚(GPIO45和GPIO46)做输出,分别控制两个电机的抱闸机构:

- 当GPIO45和46的GPBDAT寄存器写1时,电机的抱闸机构松开,电机可以运行。

- 当GPIO45和46的GPBDAT寄存器写0时,电机的抱闸机构闭合,电机被锁止。

- 控制板上电初始化阶段,对GPIO45和46的GPBDAT寄存器写0,电机处于被锁止的状态。

遇到的问题:

控制板搭载在设备上使用约两个月的时间,出现了一个奇怪的问题,(当然,没有奇怪的问题,只有未解的谜团)。每次给设备上电后,GPIO45和46的GPBDAT状态读取出来是1,导致两个电机的抱闸机构松开,电机无法被锁止。但是只要上位机发指令操作一次GPBDAT寄存器写0,GPIO的状态就正常了,后续运行中状态也一直受控。直到断电后再次上电状态异常。

测试:

为了验证GPIO45、46管脚的状态,把GPIO45和46管脚的外围电路断开,使这两个管脚悬空。另外把预留的两个管脚GPIO40和41也配置为输出,与故障的45和46管脚状态做对比。

把GPIO40,41,45,46的GPBDAT寄存器状态都用CAN监控。得到以下结果:

(1)初始化赋值

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

烧写程序后,给控制器断电再上电(不是仿真,是用CAN监控GPBDAT寄存器状态),如下

(2)上电后的GPIO管脚状态:

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 1;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

(3)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO46 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO46 = 0;

(4)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO45 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

(5)后续对GpioDataRegs.GPBDAT.bit.GPIO45 和46的操作均正常。

说明:

通过GPIO40,41与GPIO45,46的对比,可以看出GPIO40,41上电初始化后的状态受控。但是GPIO45,46的状态恒为1,但是程序运行中其状态也受GPBDAT寄存器的控制。

问题:

上面这种情况是否说明DSP的GPIO45,46管脚已经有问题了?

如果管脚损坏了,是哪方面原因使其损坏的?该从哪方面去查原因?

Young Hu:有两个提示:

1.上电以后GPIO12–GPIO87默认上拉;

2.拉高GPIO,建议使用GPIOSET,拉低使用GPIOclear

最近在用28335做电机控制器,遇到了一个比较奇怪的问题。

设计目的:

用两个GPIO管脚(GPIO45和GPIO46)做输出,分别控制两个电机的抱闸机构:

- 当GPIO45和46的GPBDAT寄存器写1时,电机的抱闸机构松开,电机可以运行。

- 当GPIO45和46的GPBDAT寄存器写0时,电机的抱闸机构闭合,电机被锁止。

- 控制板上电初始化阶段,对GPIO45和46的GPBDAT寄存器写0,电机处于被锁止的状态。

遇到的问题:

控制板搭载在设备上使用约两个月的时间,出现了一个奇怪的问题,(当然,没有奇怪的问题,只有未解的谜团)。每次给设备上电后,GPIO45和46的GPBDAT状态读取出来是1,导致两个电机的抱闸机构松开,电机无法被锁止。但是只要上位机发指令操作一次GPBDAT寄存器写0,GPIO的状态就正常了,后续运行中状态也一直受控。直到断电后再次上电状态异常。

测试:

为了验证GPIO45、46管脚的状态,把GPIO45和46管脚的外围电路断开,使这两个管脚悬空。另外把预留的两个管脚GPIO40和41也配置为输出,与故障的45和46管脚状态做对比。

把GPIO40,41,45,46的GPBDAT寄存器状态都用CAN监控。得到以下结果:

(1)初始化赋值

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

烧写程序后,给控制器断电再上电(不是仿真,是用CAN监控GPBDAT寄存器状态),如下

(2)上电后的GPIO管脚状态:

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 1;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

(3)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO46 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO46 = 0;

(4)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO45 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

(5)后续对GpioDataRegs.GPBDAT.bit.GPIO45 和46的操作均正常。

说明:

通过GPIO40,41与GPIO45,46的对比,可以看出GPIO40,41上电初始化后的状态受控。但是GPIO45,46的状态恒为1,但是程序运行中其状态也受GPBDAT寄存器的控制。

问题:

上面这种情况是否说明DSP的GPIO45,46管脚已经有问题了?

如果管脚损坏了,是哪方面原因使其损坏的?该从哪方面去查原因?

user5897540:

回复 Young Hu:

非常感谢,有以下问题:

1,虽然上电以后GPIO12–GPIO87默认上拉,但是(1)我的程序是把上电以后GPIO40、41、45、46单独初始化为拉低。所以上电初始化完成后这四个管脚的状态应该是拉低的。由GPIO40和41的测试可以验证这一点,(2)同样其他几个板子也可以把GPIO45、46初始化为拉低。(3)出问题的这个板子刚开始的时候也是没有这个问题的,使用了两个月后GPIO45、46才出现了这样的异常。

2,测试中也使用过GPIOSET和GPIOclear,测试效果并没有改善。

现在担心的是这个板子出了这个问题,找不到原因,可能其他的板子以后也会出问题。

最近在用28335做电机控制器,遇到了一个比较奇怪的问题。

设计目的:

用两个GPIO管脚(GPIO45和GPIO46)做输出,分别控制两个电机的抱闸机构:

- 当GPIO45和46的GPBDAT寄存器写1时,电机的抱闸机构松开,电机可以运行。

- 当GPIO45和46的GPBDAT寄存器写0时,电机的抱闸机构闭合,电机被锁止。

- 控制板上电初始化阶段,对GPIO45和46的GPBDAT寄存器写0,电机处于被锁止的状态。

遇到的问题:

控制板搭载在设备上使用约两个月的时间,出现了一个奇怪的问题,(当然,没有奇怪的问题,只有未解的谜团)。每次给设备上电后,GPIO45和46的GPBDAT状态读取出来是1,导致两个电机的抱闸机构松开,电机无法被锁止。但是只要上位机发指令操作一次GPBDAT寄存器写0,GPIO的状态就正常了,后续运行中状态也一直受控。直到断电后再次上电状态异常。

测试:

为了验证GPIO45、46管脚的状态,把GPIO45和46管脚的外围电路断开,使这两个管脚悬空。另外把预留的两个管脚GPIO40和41也配置为输出,与故障的45和46管脚状态做对比。

把GPIO40,41,45,46的GPBDAT寄存器状态都用CAN监控。得到以下结果:

(1)初始化赋值

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

烧写程序后,给控制器断电再上电(不是仿真,是用CAN监控GPBDAT寄存器状态),如下

(2)上电后的GPIO管脚状态:

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 1;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

(3)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO46 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO46 = 0;

(4)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO45 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

(5)后续对GpioDataRegs.GPBDAT.bit.GPIO45 和46的操作均正常。

说明:

通过GPIO40,41与GPIO45,46的对比,可以看出GPIO40,41上电初始化后的状态受控。但是GPIO45,46的状态恒为1,但是程序运行中其状态也受GPBDAT寄存器的控制。

问题:

上面这种情况是否说明DSP的GPIO45,46管脚已经有问题了?

如果管脚损坏了,是哪方面原因使其损坏的?该从哪方面去查原因?

mangui zhang:

回复 user5897540:

肯定是IO损坏了IO口与一些外设连接最好做一些匹配和保护等设计

最近在用28335做电机控制器,遇到了一个比较奇怪的问题。

设计目的:

用两个GPIO管脚(GPIO45和GPIO46)做输出,分别控制两个电机的抱闸机构:

- 当GPIO45和46的GPBDAT寄存器写1时,电机的抱闸机构松开,电机可以运行。

- 当GPIO45和46的GPBDAT寄存器写0时,电机的抱闸机构闭合,电机被锁止。

- 控制板上电初始化阶段,对GPIO45和46的GPBDAT寄存器写0,电机处于被锁止的状态。

遇到的问题:

控制板搭载在设备上使用约两个月的时间,出现了一个奇怪的问题,(当然,没有奇怪的问题,只有未解的谜团)。每次给设备上电后,GPIO45和46的GPBDAT状态读取出来是1,导致两个电机的抱闸机构松开,电机无法被锁止。但是只要上位机发指令操作一次GPBDAT寄存器写0,GPIO的状态就正常了,后续运行中状态也一直受控。直到断电后再次上电状态异常。

测试:

为了验证GPIO45、46管脚的状态,把GPIO45和46管脚的外围电路断开,使这两个管脚悬空。另外把预留的两个管脚GPIO40和41也配置为输出,与故障的45和46管脚状态做对比。

把GPIO40,41,45,46的GPBDAT寄存器状态都用CAN监控。得到以下结果:

(1)初始化赋值

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

烧写程序后,给控制器断电再上电(不是仿真,是用CAN监控GPBDAT寄存器状态),如下

(2)上电后的GPIO管脚状态:

GpioDataRegs.GPBDAT.bit.GPIO40 = 0;

GpioDataRegs.GPBDAT.bit.GPIO41 = 1

GpioDataRegs.GPBDAT.bit.GPIO45 = 1;

GpioDataRegs.GPBDAT.bit.GPIO46 = 1;

(3)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO46 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO46 = 0;

(4)用CAN指令进行GpioDataRegs.GPBDAT.bit.GPIO45 = 0;的操作后:

GpioDataRegs.GPBDAT.bit.GPIO45 = 0;

(5)后续对GpioDataRegs.GPBDAT.bit.GPIO45 和46的操作均正常。

说明:

通过GPIO40,41与GPIO45,46的对比,可以看出GPIO40,41上电初始化后的状态受控。但是GPIO45,46的状态恒为1,但是程序运行中其状态也受GPBDAT寄存器的控制。

问题:

上面这种情况是否说明DSP的GPIO45,46管脚已经有问题了?

如果管脚损坏了,是哪方面原因使其损坏的?该从哪方面去查原因?

user5897540:

回复 mangui zhang:

感谢!!!

请教大神以前遇到过类似情况吗?我这两个管脚的硬件设计是GPIO45和46分别驱动两个三极管,三极管再驱动继电器,继电器控制电机的抱闸机构(见图所示)。如果外设部分有隐患,有可能通过三极管损坏GPIO管脚吗?

TI中文支持网

TI中文支持网