大家好,

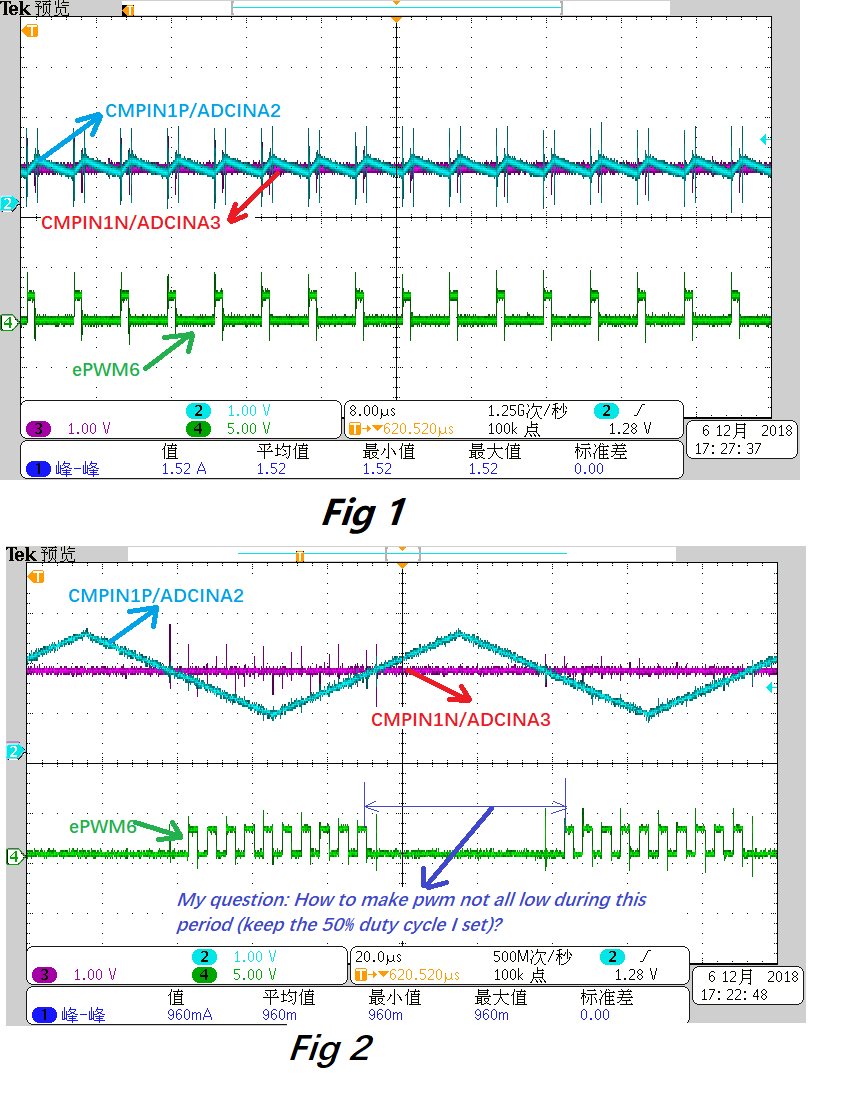

我想用CMPSS实现降压转换器的峰值电流模式控制。 因此,我编写了一些代码来测试CMPSS和ePWM。 测试波形如下,其中浅蓝色线表示CMPIN1P / ADCINA2中连接的信号,粉色线表示CMPIN1N / ADCINA3中连接的信号。 绿线是输出信号(ePWM6A)。

在代码中,我将默认占空比设置为50%,并在CMPSS跳闸事件发生时强制为低。 图1给出了CMPSS工作的波形,它可以强制PWM为低电平。 但是,根据图2,当CMPIN1P> CMPIN1N时,ePWM总是很低,这不是我想要的。 我希望在CMPIN1P> CMPIN1N期间,PWM总是输出我设置的占空比(50%而不是总是低)。 代码如下所示,我应该如何设置寄存器? 谢谢!

void InitEPwm6Example(void)

{EPwm6Regs.TBPRD = 500;// Set timer periodEPwm6Regs.TBPHS.bit.TBPHS = 0x0000;// Phase is 0EPwm6Regs.TBCTR = 0x0000;// Clear counter//// Setup TBCLK//EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count upEPwm6Regs.TBCTL.bit.PHSEN = TB_DISABLE;// Disable phase loadingEPwm6Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;// Clock ratio to SYSCLKOUTEPwm6Regs.TBCTL.bit.CLKDIV = TB_DIV1;// Slow just to observe on// the scope.EPwm6Regs.TBCTL.bit.PHSEN = TB_ENABLE;//禁止相位控制EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW;//TBPRD寄存器采用映射模式EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //禁止同步信号// Setup compare//EPwm6Regs.CMPA.bit.CMPA = 250;//计数到此,强制拉低//// Set actions//EPwm6Regs.AQCTLA.bit.ZRO = AQ_SET;//在计数为0处,设置EPWMA为高电平EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR;// 达到设定计数值CMPA处,EPWMA为低电平///----------------------------------------------------------------------------EALLOW;//Configure DCB to be TRIP4EPwm6Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 3;//选择Zone4 作为触发Trip 4EPwm6Regs.TZDCSEL.bit.DCBEVT2 = TZ_DCBH_HI;//Digital compare output B event 2 选择EPwm6Regs.TZSEL.bit.DCBEVT2 = 1;//Configure DCB as CBC//Configure DCB path to be filtered & asyncEPwm6Regs.DCBCTL.bit.EVT2SRCSEL = DC_EVT_FLT;// Source is DCBEVT2 SignaEPwm6Regs.DCBCTL.bit.EVT2FRCSYNCSEL = DC_EVT_SYNC;// 0: Source Is Synchronous Signal//空窗设置EPwm6Regs.DCFCTL.bit.BLANKE=1;//1: Blanking window is enabledEPwm6Regs.DCFCTL.bit.PULSESEL=2;// Time-base counter equal to zero (TBCTR = 0x00)EPwm6Regs.DCFCTL.bit.SRCSEL=3;// Source Is DCBEVT2 SignalEPwm6Regs.DCFOFFSET=0;//Blanking Window OffsetEPwm6Regs.DCFWINDOW=30;//0.1 us 20EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX0 = 1; //Enable TRIP4 Mux for OutputEPwm6Regs.TZCTL.bit.TZA=TZ_FORCE_LO;// Force EPWMxA to a low stateEPwm6Regs.TZCLR.bit.CBCPULSE=0;//CTR = zero pulse clears CBC trip latch. (Same as legacy designs.)EPwmXbarRegs.TRIP5MUXENABLE.bit.MUX0 = 1; //Enable TRIP4 Mux for OutputEDIS;

}

//

// InitCMPSS - Initialize CMPSS1 and configure settings

//

void InitCMPSS(void)

{EALLOW;////Enable CMPSS//Cmpss1Regs.COMPCTL.bit.COMPDACE = 1;////NEG signal comes from DAC//Cmpss1Regs.COMPCTL.bit.COMPHSOURCE = NEGIN_PIN;////Use VDDA as the reference for DAC//Cmpss1Regs.COMPDACCTL.bit.SELREF = REFERENCE_VDDA;////Set DAC to midpoint for arbitrary reference//

//Cmpss1Regs.DACHVALS.bit.DACVAL = 800;//// Configure CTRIPOUT path// Asynch output feeds CTRIPH and CTRIPOUTH//

//Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_SYNCH;

//Cmpss1Regs.COMPCTL.bit.CTRIPOUTHSEL = CTRIP_SYNCH;EDIS;

}

Joey Zhang1994:你好,请问你的问题解决了吗?是如何解决的呢?我最近也遇到了类似的问题,请多指教,谢谢!

TI中文支持网

TI中文支持网