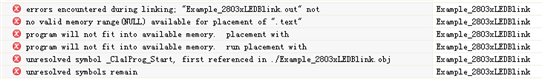

今天尝试了在项目里添加了cla 程序后出现分配不了空间问题,不能链接了,问题如下:

使用的是系统的CMD文件 28035_RAM_CLA_lnk.cmd,没做任何改动,编译器版本为6.2 请帮忙分析一下,谢谢!

/*

//###########################################################################

//

// FILE: 28035_RAM_CLA_lnk.cmd

//

// TITLE: Linker Command File For 28035 examples that run out of RAM

//

// This ONLY includes all SARAM blocks on the 28035 device.

// This does not include flash or OTP.

//

// Keep in mind that L0,L1,L2, and L3 are protected by the code

// security module.

//

// What this means is in most cases you will want to move to

// another memory map file which has more memory defined.

//

//###########################################################################

// $TI Release: F2803x C/C++ Header Files and Peripheral Examples V126 $

// $Release Date: November 30, 2011 $

//###########################################################################

*/

/* ======================================================

// For Code Composer Studio V2.2 and later

// —————————————

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

//

// The header linker files are found in <base>\DSP2803x_headers\cmd

//

// For BIOS applications add: DSP2803x_Headers_BIOS.cmd

// For nonBIOS applications add: DSP2803x_Headers_nonBIOS.cmd

========================================================= */

/* ======================================================

// For Code Composer Studio prior to V2.2

// ————————————–

// 1) Use one of the following -l statements to include the

// header linker command file in the project. The header linker

// file is required to link the peripheral structures to the proper

// locations within the memory map */

/* Uncomment this line to include file only for non-BIOS applications */

/* -l DSP2803x_Headers_nonBIOS.cmd */

/* Uncomment this line to include file only for BIOS applications */

/* -l DSP2803x_Headers_BIOS.cmd */

/* 2) In your project add the path to <base>\DSP2803x_headers\cmd to the

library search path under project->build options, linker tab,

library search path (-i).

/*========================================================= */

/* Define the memory block start/length for the DSP2803x

PAGE 0 will be used to organize program sections

PAGE 1 will be used to organize data sections

Notes:

Memory blocks on F28035 are uniform (ie same

physical memory) in both PAGE 0 and PAGE 1.

That is the same memory region should not be

defined for both PAGE 0 and PAGE 1.

Doing so will result in corruption of program

and/or data.

L0 block is mirrored – that is it

can be accessed in high memory or low memory.

For simplicity only one instance is used in this

linker file.

Contiguous SARAM memory blocks can be combined

if required to create a larger memory block.

*/

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to SARAM" bootloader mode */

BEGIN : origin = 0x000000, length = 0x000002

RAMM0 : origin = 0x000050, length = 0x0003B0

RAML0L1 : origin = 0x008000, length = 0x000C00

RAML3 : origin = 0x009000, length = 0x001000

RESET : origin = 0x3FFFC0, length = 0x000002

IQTABLES : origin = 0x3FE000, length = 0x000B50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

BOOTROM : origin = 0x3FF27C, length = 0x000D44

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x00004E /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000480, length = 0x000380 /* on-chip RAM block M1 */

RAML2 : origin = 0x008C00, length = 0x000400

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

/* Setup for "boot to SARAM" mode:

The codestart section (found in DSP28_CodeStartBranch.asm)

re-directs execution to the start of user code. */

codestart : > BEGIN, PAGE = 0

ramfuncs : > RAMM0 PAGE = 0

.text : > RAML0L1, PAGE = 0

.cinit : > RAMM0, PAGE = 0

.pinit : > RAMM0, PAGE = 0

.switch : > RAMM0, PAGE = 0

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.stack : > RAMM1, PAGE = 1

.ebss : > RAML2, PAGE = 1

.econst : > RAML2, PAGE = 1

.esysmem : > RAML2, PAGE = 1

IQmath : > RAML0L1, PAGE = 0

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

Cla1Prog : LOAD = RAML0L1,

RUN = RAML3,

LOAD_START(_Cla1funcsLoadStart),

LOAD_SIZE(_Cla1funcsLoadSize)

RUN_START(_Cla1funcsRunStart),

PAGE = 0

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)

}

*/

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

map文件如下:

******************************************************************************

TMS320C2000 Linker PC v6.1.0******************************************************************************

>> Linked Sun Apr 13 22:31:12 2014

OUTPUT FILE NAME: <Example_2803xLEDBlink.out>

ENTRY POINT SYMBOL: "code_start" address: 00000000

MEMORY CONFIGURATION

name origin length used unused attr fill

———————- ——– ——— ——– ——– —- ——–

PAGE 1:

DEV_EMU 00000880 00000105 00000076 0000008f RWIX

SYS_PWR_CTL 00000985 00000003 00000003 00000000 RWIX

FLASH_REGS 00000a80 00000060 00000008 00000058 RWIX

CSM 00000ae0 00000010 00000010 00000000 RWIX

ADC_RESULT 00000b00 00000020 00000020 00000000 RWIX

CPU_TIMER0 00000c00 00000008 00000008 00000000 RWIX

CPU_TIMER1 00000c08 00000008 00000008 00000000 RWIX

CPU_TIMER2 00000c10 00000008 00000008 00000000 RWIX

PIE_CTRL 00000ce0 00000020 0000001a 00000006 RWIX

PIE_VECT 00000d00 00000100 00000100 00000000 RWIX

CLA1 00001400 00000080 00000040 00000040 RWIX

ECANA 00006000 00000040 00000034 0000000c RWIX

ECANA_LAM 00006040 00000040 00000040 00000000 RWIX

ECANA_MOTS 00006080 00000040 00000040 00000000 RWIX

ECANA_MOTO 000060c0 00000040 00000040 00000000 RWIX

ECANA_MBOX 00006100 00000100 00000100 00000000 RWIX

COMP1 00006400 00000020 00000014 0000000c RWIX

COMP2 00006420 00000020 00000014 0000000c RWIX

COMP3 00006440 00000020 00000014 0000000c RWIX

EPWM1 00006800 00000040 00000040 00000000 RWIX

EPWM2 00006840 00000040 00000040 00000000 RWIX

EPWM3 00006880 00000040 00000040 00000000 RWIX

EPWM4 000068c0 00000040 00000040 00000000 RWIX

EPWM5 00006900 00000040 00000040 00000000 RWIX

EPWM6 00006940 00000040 00000040 00000000 RWIX

EPWM7 00006980 00000040 00000040 00000000 RWIX

ECAP1 00006a00 00000020 00000020 00000000 RWIX

HRCAP1 00006ac0 00000020 00000020 00000000 RWIX

HRCAP2 00006ae0 00000020 00000020 00000000 RWIX

EQEP1 00006b00 00000040 00000040 00000000 RWIX

LINA 00006c00 00000080 0000004a 00000036 RWIX

GPIOCTRL 00006f80 00000040 00000040 00000000 RWIX

GPIODAT 00006fc0 00000020 00000020 00000000 RWIX

GPIOINT 00006fe0 00000020 0000000c 00000014 RWIX

SYSTEM 00007010 00000020 00000020 00000000 RWIX

SPIA 00007040 00000010 00000010 00000000 RWIX

SCIA 00007050 00000010 00000010 00000000 RWIX

NMIINTRUPT 00007060 00000010 00000010 00000000 RWIX

XINTRUPT 00007070 00000010 00000010 00000000 RWIX

ADC 00007100 00000080 00000050 00000030 RWIX

SPIB 00007740 00000010 00000010 00000000 RWIX

I2CA 00007900 00000040 00000022 0000001e RWIX

PARTID 003d7e80 00000001 00000001 00000000 RWIX

CSM_PWL 003f7ff8 00000008 00000008 00000000 RWIX

SECTION ALLOCATION MAP

output attributes/

section page origin length input sections

——– —- ———- ———- —————-

codestart* 0 00000000 00000002 FAILED TO ALLOCATE

.text 0 00000000 00000ba9 FAILED TO ALLOCATE

Cla1Prog 0 00000000 00000040 FAILED TO ALLOCATE

.cinit 0 00000000 00000079 FAILED TO ALLOCATE

ramfuncs 0 00000000 0000001f FAILED TO ALLOCATE

.econst 0 00000000 00000100 FAILED TO ALLOCATE

.stack 0 00000000 00000200 FAILED TO ALLOCATE

.reset 0 00000000 00000002 FAILED TO ALLOCATE

DevEmuRegsFile* 1 00000880 00000004 UNINITIALIZED

00000880 00000004 DSP2803x_GlobalVariableDefs.obj (DevEmuRegsFile)

.ebss 1 00000884 0000006c UNINITIALIZED

00000884 00000030 Example_2803xLEDBlink.obj (.ebss)

000008b4 00000006 MainTimer.obj (.ebss)

000008ba 00000004 rts2800_ml.lib : _lock.obj (.ebss)

000008be 00000002 –HOLE–

000008c0 00000018 DSP2803x_CpuTimers.obj (.ebss)

000008d8 00000014 motor2_shared_data.obj (.ebss)

000008ec 00000004 rts2800_ml.lib : exit.obj (.ebss)

CpuToCla1MsgRAM* 1 000008f0 00000004 UNINITIALIZED

000008f0 00000004 motor2_shared_data.obj (CpuToCla1MsgRAM)

Cla1ToCpuMsgRAM* 1 000008f4 00000002 UNINITIALIZED

000008f4 00000002 motor2_shared_data.obj (Cla1ToCpuMsgRAM)

SysPwrCtrlRegsFile* 1 00000985 00000003 UNINITIALIZED

00000985 00000003 DSP2803x_GlobalVariableDefs.obj (SysPwrCtrlRegsFile)

FlashRegsFile* 1 00000a80 00000008 UNINITIALIZED

00000a80 00000008 DSP2803x_GlobalVariableDefs.obj (FlashRegsFile)

CsmRegsFile* 1 00000ae0 00000010 UNINITIALIZED

00000ae0 00000010 DSP2803x_GlobalVariableDefs.obj (CsmRegsFile)

AdcResultFile* 1 00000b00 00000020 UNINITIALIZED

00000b00 00000020 DSP2803x_GlobalVariableDefs.obj (AdcResultFile)

CpuTimer0RegsFile* 1 00000c00 00000008 UNINITIALIZED

00000c00 00000008 DSP2803x_GlobalVariableDefs.obj (CpuTimer0RegsFile)

CpuTimer1RegsFile* 1 00000c08 00000008 UNINITIALIZED

00000c08 00000008 DSP2803x_GlobalVariableDefs.obj (CpuTimer1RegsFile)

CpuTimer2RegsFile* 1 00000c10 00000008 UNINITIALIZED

00000c10 00000008 DSP2803x_GlobalVariableDefs.obj (CpuTimer2RegsFile)

PieCtrlRegsFile* 1 00000ce0 0000001a UNINITIALIZED

00000ce0 0000001a DSP2803x_GlobalVariableDefs.obj (PieCtrlRegsFile)

PieVectTableFile* 1 00000d00 00000100 UNINITIALIZED

00000d00 00000100 DSP2803x_GlobalVariableDefs.obj (PieVectTableFile)

EmuKeyVar* 1 00000d00 00000001 UNINITIALIZED

00000d00 00000001 DSP2803x_GlobalVariableDefs.obj (EmuKeyVar)

EmuBModeVar* 1 00000d01 00000001 UNINITIALIZED

00000d01 00000001 DSP2803x_GlobalVariableDefs.obj (EmuBModeVar)

FlashCallbackVar* 1 00000d02 00000002 UNINITIALIZED

00000d02 00000002 DSP2803x_GlobalVariableDefs.obj (FlashCallbackVar)

FlashScalingVar* 1 00000d04 00000002 UNINITIALIZED

00000d04 00000002 DSP2803x_GlobalVariableDefs.obj (FlashScalingVar)

Cla1RegsFile* 1 00001400 00000040 UNINITIALIZED

00001400 00000040 DSP2803x_GlobalVariableDefs.obj (Cla1RegsFile)

ECanaRegsFile* 1 00006000 00000034 UNINITIALIZED

00006000 00000034 DSP2803x_GlobalVariableDefs.obj (ECanaRegsFile)

ECanaLAMRegsFile* 1 00006040 00000040 UNINITIALIZED

00006040 00000040 DSP2803x_GlobalVariableDefs.obj (ECanaLAMRegsFile)

ECanaMOTSRegsFile* 1 00006080 00000040 UNINITIALIZED

00006080 00000040 DSP2803x_GlobalVariableDefs.obj (ECanaMOTSRegsFile)

ECanaMOTORegsFile* 1 000060c0 00000040 UNINITIALIZED

000060c0 00000040 DSP2803x_GlobalVariableDefs.obj (ECanaMOTORegsFile)

ECanaMboxesFile* 1 00006100 00000100 UNINITIALIZED

00006100 00000100 DSP2803x_GlobalVariableDefs.obj (ECanaMboxesFile)

Comp1RegsFile* 1 00006400 00000014 UNINITIALIZED

00006400 00000014 DSP2803x_GlobalVariableDefs.obj (Comp1RegsFile)

Comp2RegsFile* 1 00006420 00000014 UNINITIALIZED

00006420 00000014 DSP2803x_GlobalVariableDefs.obj (Comp2RegsFile)

Comp3RegsFile* 1 00006440 00000014 UNINITIALIZED

00006440 00000014 DSP2803x_GlobalVariableDefs.obj (Comp3RegsFile)

EPwm1RegsFile* 1 00006800 00000040 UNINITIALIZED

00006800 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm1RegsFile)

EPwm2RegsFile* 1 00006840 00000040 UNINITIALIZED

00006840 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm2RegsFile)

EPwm3RegsFile* 1 00006880 00000040 UNINITIALIZED

00006880 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm3RegsFile)

EPwm4RegsFile* 1 000068c0 00000040 UNINITIALIZED

000068c0 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm4RegsFile)

EPwm5RegsFile* 1 00006900 00000040 UNINITIALIZED

00006900 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm5RegsFile)

EPwm6RegsFile* 1 00006940 00000040 UNINITIALIZED

00006940 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm6RegsFile)

EPwm7RegsFile* 1 00006980 00000040 UNINITIALIZED

00006980 00000040 DSP2803x_GlobalVariableDefs.obj (EPwm7RegsFile)

ECap1RegsFile* 1 00006a00 00000020 UNINITIALIZED

00006a00 00000020 DSP2803x_GlobalVariableDefs.obj (ECap1RegsFile)

HRCap1RegsFile* 1 00006ac0 00000020 UNINITIALIZED

00006ac0 00000020 DSP2803x_GlobalVariableDefs.obj (HRCap1RegsFile)

HRCap2RegsFile* 1 00006ae0 00000020 UNINITIALIZED

00006ae0 00000020 DSP2803x_GlobalVariableDefs.obj (HRCap2RegsFile)

EQep1RegsFile* 1 00006b00 00000040 UNINITIALIZED

00006b00 00000040 DSP2803x_GlobalVariableDefs.obj (EQep1RegsFile)

LinaRegsFile* 1 00006c00 0000004a UNINITIALIZED

00006c00 0000004a DSP2803x_GlobalVariableDefs.obj (LinaRegsFile)

GpioCtrlRegsFile* 1 00006f80 00000040 UNINITIALIZED

00006f80 00000040 DSP2803x_GlobalVariableDefs.obj (GpioCtrlRegsFile)

GpioDataRegsFile* 1 00006fc0 00000020 UNINITIALIZED

00006fc0 00000020 DSP2803x_GlobalVariableDefs.obj (GpioDataRegsFile)

GpioIntRegsFile* 1 00006fe0 0000000c UNINITIALIZED

00006fe0 0000000c DSP2803x_GlobalVariableDefs.obj (GpioIntRegsFile)

SysCtrlRegsFile* 1 00007010 00000020 UNINITIALIZED

00007010 00000020 DSP2803x_GlobalVariableDefs.obj (SysCtrlRegsFile)

SpiaRegsFile* 1 00007040 00000010 UNINITIALIZED

00007040 00000010 DSP2803x_GlobalVariableDefs.obj (SpiaRegsFile)

SciaRegsFile* 1 00007050 00000010 UNINITIALIZED

00007050 00000010 DSP2803x_GlobalVariableDefs.obj (SciaRegsFile)

NmiIntruptRegsFile* 1 00007060 00000010 UNINITIALIZED

00007060 00000010 DSP2803x_GlobalVariableDefs.obj (NmiIntruptRegsFile)

XIntruptRegsFile* 1 00007070 00000010 UNINITIALIZED

00007070 00000010 DSP2803x_GlobalVariableDefs.obj (XIntruptRegsFile)

AdcRegsFile* 1 00007100 00000050 UNINITIALIZED

00007100 00000050 DSP2803x_GlobalVariableDefs.obj (AdcRegsFile)

SpibRegsFile* 1 00007740 00000010 UNINITIALIZED

00007740 00000010 DSP2803x_GlobalVariableDefs.obj (SpibRegsFile)

I2caRegsFile* 1 00007900 00000022 UNINITIALIZED

00007900 00000022 DSP2803x_GlobalVariableDefs.obj (I2caRegsFile)

PartIdRegsFile* 1 003d7e80 00000001 UNINITIALIZED

003d7e80 00000001 DSP2803x_GlobalVariableDefs.obj (PartIdRegsFile)

CsmPwlFile* 1 003f7ff8 00000008 UNINITIALIZED

003f7ff8 00000008 DSP2803x_GlobalVariableDefs.obj (CsmPwlFile)

GLOBAL SYMBOLS: SORTED ALPHABETICALLY BY Name

address name

——– —-

00000000 .text

00000a40 C$$EXIT

00000a59 FS$$DIV

00000adc FS$$MPY

00000b36 FS$$TOL

00000b5f FS$$TOU

00000b7c U$$DIV

00000b81 U$$MOD

000007f0 _ADCINT1_ISR

000007f5 _ADCINT2_ISR

000008a9 _ADCINT3_ISR

000008ae _ADCINT4_ISR

000008b3 _ADCINT5_ISR

000008b8 _ADCINT6_ISR

000008bd _ADCINT7_ISR

000008c2 _ADCINT8_ISR

00000804 _ADCINT9_ISR

00007100 _AdcRegs

00000b00 _AdcResult

000008c7 _CLA1_INT1_ISR

000008cc _CLA1_INT2_ISR

000008d1 _CLA1_INT3_ISR

000008d6 _CLA1_INT4_ISR

000008db _CLA1_INT5_ISR

000008e0 _CLA1_INT6_ISR

000008e5 _CLA1_INT7_ISR

000008ea _CLA1_INT8_ISR

UNDEFED _Cla1Prog_Start

00001400 _Cla1Regs

00000000 _Cla1Task1

00000008 _Cla1Task2

00000010 _Cla1Task3

00000018 _Cla1Task4

00000020 _Cla1Task5

00000028 _Cla1Task6

00000030 _Cla1Task7

00000038 _Cla1Task8

00006400 _Comp1Regs

00006420 _Comp2Regs

00006440 _Comp3Regs

0000094e _ConfigCpuTimer

000008d0 _CpuTimer0

00000c00 _CpuTimer0Regs

000008c0 _CpuTimer1

00000c08 _CpuTimer1Regs

000008c8 _CpuTimer2

00000c10 _CpuTimer2Regs

003f7ff8 _CsmPwl

00000ae0 _CsmRegs

000006c5 _CsmUnlock

0000079b _DATALOG_ISR

0000098b _DRV8301_SPI_Init

000009af _DRV8301_SPI_Read

000009de _DRV8301_SPI_Write

00000893 _DRV8301_cntrl_reg1

00000892 _DRV8301_cntrl_reg2

0000088b _DRV8301_stat_reg1

00000891 _DRV8301_stat_reg2

00000895 _DRV_RESET

0000001b _DSP28x_usDelay

000008f0 _Den

00000880 _DevEmuRegs

00000047 _DeviceInit

00000631 _DisableDog

00000440 _Drive_control

0000089f _ECAN0INTA_ISR

000008a4 _ECAN1INTA_ISR

00000859 _ECAP1_INT_ISR

00006040 _ECanaLAMRegs

000060c0 _ECanaMOTORegs

00006080 _ECanaMOTSRegs

00006100 _ECanaMboxes

00006000 _ECanaRegs

00006a00 _ECap1Regs

000008fe _EMPTY_ISR

000007a5 _EMUINT_ISR

00000836 _EPWM1_INT_ISR

00000813 _EPWM1_TZINT_ISR

0000083b _EPWM2_INT_ISR

00000818 _EPWM2_TZINT_ISR

00000840 _EPWM3_INT_ISR

0000081d _EPWM3_TZINT_ISR

00000845 _EPWM4_INT_ISR

00000822 _EPWM4_TZINT_ISR

0000084a _EPWM5_INT_ISR

00000827 _EPWM5_TZINT_ISR

0000084f _EPWM6_INT_ISR

0000082c _EPWM6_TZINT_ISR

00000854 _EPWM7_INT_ISR

00000831 _EPWM7_TZINT_ISR

00006800 _EPwm1Regs

00006840 _EPwm2Regs

00006880 _EPwm3Regs

000068c0 _EPwm4Regs

00006900 _EPwm5Regs

00006940 _EPwm6Regs

00006980 _EPwm7Regs

00000868 _EQEP1_INT_ISR

00006b00 _EQep1Regs

00000d01 _EmuBMode

00000d00 _EmuKey

0000088d _EnableFlag

00000788 _EnableInterrupts

0000072e _ExtOscSel

00000a80 _FlashRegs

00000d04 _Flash_CPUScaleFactor

00000d02 _Flash_CallbackPtr

00006f80 _GpioCtrlRegs

00006fc0 _GpioDataRegs

00006fe0 _GpioIntRegs

0000085e _HRCAP1_INT_ISR

00000863 _HRCAP2_INT_ISR

00006ac0 _HRCap1Regs

00006ae0 _HRCap2Regs

00000888 _HallGpioBitA

00000887 _HallGpioBitB

0000088a _HallGpioBitC

0000088c _HallOffset

00000886 _HallPointer

00000890 _HallState

00000881 _I2CINT1A_ISR

00000886 _I2CINT2A_ISR

00007900 _I2caRegs

000007af _ILLEGAL_ISR

00000791 _INT13_ISR

00000796 _INT14_ISR

0000049c _ISR_ILLEGAL

0000090d _InitCpuTimers

00000000 _InitFlash

00000689 _InitPeripheralClocks

00000769 _InitPieCtrl

00000744 _InitPieVectTable

00000639 _InitPll

0000060d _InitSysCtrl

000006f6 _IntOsc1Sel

00000706 _IntOsc2Sel

00000895 _LIN0INTA_ISR

0000089a _LIN1INTA_ISR

000008f9 _LUF_ISR

000008f4 _LVF_ISR

00006c00 _LinaRegs

0000001b _MainTimer

000001aa _MemCopy

000007aa _NMI_ISR

00007060 _NmiIntruptRegs

000008f2 _Num

00000903 _PIE_RESERVED

00000174 _PLLset

003d7e80 _PartIdRegs

00000ce0 _PieCtrlRegs

00000d00 _PieVectTable

00000000 _PieVectTableInit

000007a0 _RTOSINT_ISR

000008f4 _Res

0000088f _RunMotor

0000088b _SCIRXINTA_ISR

00000890 _SCITXINTA_ISR

0000086d _SPIRXINTA_ISR

00000877 _SPIRXINTB_ISR

00000872 _SPITXINTA_ISR

0000087c _SPITXINTB_ISR

00007050 _SciaRegs

00000627 _ServiceDog

00007040 _SpiaRegs

00007740 _SpibRegs

00007010 _SysCtrlRegs

00000985 _SysPwrCtrlRegs

00000898 _T

00000809 _TINT0_ISR

00000019 _Task100ms

00000002 _Task10ms

00000001 _Task1ms

0000001a _Task1s

00000000 _Task200us

00000017 _Task20ms

00000018 _Task50ms

000008b4 _Timer100ms

000008b6 _Timer10ms

000008b8 _Timer1ms

000008b5 _Timer1s

000008b7 _Timer200us

000008b9 _Timer50us

000007e1 _USER10_ISR

000007e6 _USER11_ISR

000007eb _USER12_ISR

000007b4 _USER1_ISR

000007b9 _USER2_ISR

000007be _USER3_ISR

000007c3 _USER4_ISR

000007c8 _USER5_ISR

000007cd _USER6_ISR

000007d2 _USER7_ISR

000007d7 _USER8_ISR

000007dc _USER9_ISR

0000080e _WAKEINT_ISR

0000016c _WDogDisable

000007fa _XINT1_ISR

000007ff _XINT2_ISR

000008ef _XINT3_ISR

00007070 _XIntruptRegs

0000071a _XtalOscSel

00000200 __STACK_END

00000200 __STACK_SIZE

00000001 __TI_args_main

ffffffff ___binit__

ffffffff ___c_args__

00000000 ___cinit__

00000ba9 ___etext__

ffffffff ___pinit__

00000000 ___text__

00000b90 __args_main

000008ec __cleanup_ptr

000008ee __dtors_ptr

000008bc __lock

00000b8f __nop

00000b8b __register_lock

00000b87 __register_unlock

00000000 __stack

000008ba __unlock

00000a40 _abort

000009fc _c_int00

000005fb _cla1_task1_isr

00000604 _cla1_task2_isr

000004a1 _cpu_timer0_isr

00000a42 _exit

000008a2 _hall1

0000088e _hallCommutateFlag

00000884 _i

00000896 _iqPosDuty

000001bf _main

0000089c _pwmcntl1

00000894 _read_drv_status

00000908 _rsvd_ISR

0000089a _temp

00000889 _uiNegDuty

00000885 _uiPosDuty

000008d8 _y

ffffffff binit

00000000 cinit

00000000 code_start

00000ba9 etext

ffffffff pinit

GLOBAL SYMBOLS: SORTED BY Symbol Address

address name

——– —-

00000000 .text

00000000 _Cla1Task1

00000000 _InitFlash

00000000 _PieVectTableInit

00000000 _Task200us

00000000 ___cinit__

00000000 ___text__

00000000 __stack

00000000 cinit

00000000 code_start

00000001 _Task1ms

00000001 __TI_args_main

00000002 _Task10ms

00000008 _Cla1Task2

00000010 _Cla1Task3

00000017 _Task20ms

00000018 _Cla1Task4

00000018 _Task50ms

00000019 _Task100ms

0000001a _Task1s

0000001b _DSP28x_usDelay

0000001b _MainTimer

00000020 _Cla1Task5

00000028 _Cla1Task6

00000030 _Cla1Task7

00000038 _Cla1Task8

00000047 _DeviceInit

0000016c _WDogDisable

00000174 _PLLset

000001aa _MemCopy

000001bf _main

00000200 __STACK_END

00000200 __STACK_SIZE

00000440 _Drive_control

0000049c _ISR_ILLEGAL

000004a1 _cpu_timer0_isr

000005fb _cla1_task1_isr

00000604 _cla1_task2_isr

0000060d _InitSysCtrl

00000627 _ServiceDog

00000631 _DisableDog

00000639 _InitPll

00000689 _InitPeripheralClocks

000006c5 _CsmUnlock

000006f6 _IntOsc1Sel

00000706 _IntOsc2Sel

0000071a _XtalOscSel

0000072e _ExtOscSel

00000744 _InitPieVectTable

00000769 _InitPieCtrl

00000788 _EnableInterrupts

00000791 _INT13_ISR

00000796 _INT14_ISR

0000079b _DATALOG_ISR

000007a0 _RTOSINT_ISR

000007a5 _EMUINT_ISR

000007aa _NMI_ISR

000007af _ILLEGAL_ISR

000007b4 _USER1_ISR

000007b9 _USER2_ISR

000007be _USER3_ISR

000007c3 _USER4_ISR

000007c8 _USER5_ISR

000007cd _USER6_ISR

000007d2 _USER7_ISR

000007d7 _USER8_ISR

000007dc _USER9_ISR

000007e1 _USER10_ISR

000007e6 _USER11_ISR

000007eb _USER12_ISR

000007f0 _ADCINT1_ISR

000007f5 _ADCINT2_ISR

000007fa _XINT1_ISR

000007ff _XINT2_ISR

00000804 _ADCINT9_ISR

00000809 _TINT0_ISR

0000080e _WAKEINT_ISR

00000813 _EPWM1_TZINT_ISR

00000818 _EPWM2_TZINT_ISR

0000081d _EPWM3_TZINT_ISR

00000822 _EPWM4_TZINT_ISR

00000827 _EPWM5_TZINT_ISR

0000082c _EPWM6_TZINT_ISR

00000831 _EPWM7_TZINT_ISR

00000836 _EPWM1_INT_ISR

0000083b _EPWM2_INT_ISR

00000840 _EPWM3_INT_ISR

00000845 _EPWM4_INT_ISR

0000084a _EPWM5_INT_ISR

0000084f _EPWM6_INT_ISR

00000854 _EPWM7_INT_ISR

00000859 _ECAP1_INT_ISR

0000085e _HRCAP1_INT_ISR

00000863 _HRCAP2_INT_ISR

00000868 _EQEP1_INT_ISR

0000086d _SPIRXINTA_ISR

00000872 _SPITXINTA_ISR

00000877 _SPIRXINTB_ISR

0000087c _SPITXINTB_ISR

00000880 _DevEmuRegs

00000881 _I2CINT1A_ISR

00000884 _i

00000885 _uiPosDuty

00000886 _HallPointer

00000886 _I2CINT2A_ISR

00000887 _HallGpioBitB

00000888 _HallGpioBitA

00000889 _uiNegDuty

0000088a _HallGpioBitC

0000088b _DRV8301_stat_reg1

0000088b _SCIRXINTA_ISR

0000088c _HallOffset

0000088d _EnableFlag

0000088e _hallCommutateFlag

0000088f _RunMotor

00000890 _HallState

00000890 _SCITXINTA_ISR

00000891 _DRV8301_stat_reg2

00000892 _DRV8301_cntrl_reg2

00000893 _DRV8301_cntrl_reg1

00000894 _read_drv_status

00000895 _DRV_RESET

00000895 _LIN0INTA_ISR

00000896 _iqPosDuty

00000898 _T

0000089a _LIN1INTA_ISR

0000089a _temp

0000089c _pwmcntl1

0000089f _ECAN0INTA_ISR

000008a2 _hall1

000008a4 _ECAN1INTA_ISR

000008a9 _ADCINT3_ISR

000008ae _ADCINT4_ISR

000008b3 _ADCINT5_ISR

000008b4 _Timer100ms

000008b5 _Timer1s

000008b6 _Timer10ms

000008b7 _Timer200us

000008b8 _ADCINT6_ISR

000008b8 _Timer1ms

000008b9 _Timer50us

000008ba __unlock

000008bc __lock

000008bd _ADCINT7_ISR

000008c0 _CpuTimer1

000008c2 _ADCINT8_ISR

000008c7 _CLA1_INT1_ISR

000008c8 _CpuTimer2

000008cc _CLA1_INT2_ISR

000008d0 _CpuTimer0

000008d1 _CLA1_INT3_ISR

000008d6 _CLA1_INT4_ISR

000008d8 _y

000008db _CLA1_INT5_ISR

000008e0 _CLA1_INT6_ISR

000008e5 _CLA1_INT7_ISR

000008ea _CLA1_INT8_ISR

000008ec __cleanup_ptr

000008ee __dtors_ptr

000008ef _XINT3_ISR

000008f0 _Den

000008f2 _Num

000008f4 _LVF_ISR

000008f4 _Res

000008f9 _LUF_ISR

000008fe _EMPTY_ISR

00000903 _PIE_RESERVED

00000908 _rsvd_ISR

0000090d _InitCpuTimers

0000094e _ConfigCpuTimer

00000985 _SysPwrCtrlRegs

0000098b _DRV8301_SPI_Init

000009af _DRV8301_SPI_Read

000009de _DRV8301_SPI_Write

000009fc _c_int00

00000a40 C$$EXIT

00000a40 _abort

00000a42 _exit

00000a59 FS$$DIV

00000a80 _FlashRegs

00000adc FS$$MPY

00000ae0 _CsmRegs

00000b00 _AdcResult

00000b36 FS$$TOL

00000b5f FS$$TOU

00000b7c U$$DIV

00000b81 U$$MOD

00000b87 __register_unlock

00000b8b __register_lock

00000b8f __nop

00000b90 __args_main

00000ba9 ___etext__

00000ba9 etext

00000c00 _CpuTimer0Regs

00000c08 _CpuTimer1Regs

00000c10 _CpuTimer2Regs

00000ce0 _PieCtrlRegs

00000d00 _EmuKey

00000d00 _PieVectTable

00000d01 _EmuBMode

00000d02 _Flash_CallbackPtr

00000d04 _Flash_CPUScaleFactor

00001400 _Cla1Regs

00006000 _ECanaRegs

00006040 _ECanaLAMRegs

00006080 _ECanaMOTSRegs

000060c0 _ECanaMOTORegs

00006100 _ECanaMboxes

00006400 _Comp1Regs

00006420 _Comp2Regs

00006440 _Comp3Regs

00006800 _EPwm1Regs

00006840 _EPwm2Regs

00006880 _EPwm3Regs

000068c0 _EPwm4Regs

00006900 _EPwm5Regs

00006940 _EPwm6Regs

00006980 _EPwm7Regs

00006a00 _ECap1Regs

00006ac0 _HRCap1Regs

00006ae0 _HRCap2Regs

00006b00 _EQep1Regs

00006c00 _LinaRegs

00006f80 _GpioCtrlRegs

00006fc0 _GpioDataRegs

00006fe0 _GpioIntRegs

00007010 _SysCtrlRegs

00007040 _SpiaRegs

00007050 _SciaRegs

00007060 _NmiIntruptRegs

00007070 _XIntruptRegs

00007100 _AdcRegs

00007740 _SpibRegs

00007900 _I2caRegs

003d7e80 _PartIdRegs

003f7ff8 _CsmPwl

ffffffff ___binit__

ffffffff ___c_args__

ffffffff ___pinit__

ffffffff binit

ffffffff pinit

UNDEFED _Cla1Prog_Start

[242 symbols]

末末:

楼主提供的map文件提示_Cla1Prog_Start没有定义, 建议楼主先跑ControlSUITE的例程代码,在此基础上增加你的应用代码。

TI中文支持网

TI中文支持网