问题一:

在研究EPWM模块的时候,发现 其实所谓的时基同步,并不是同步的?

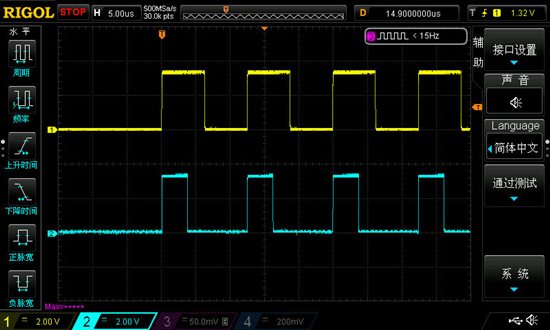

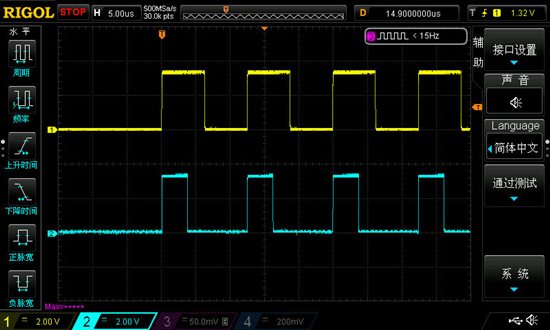

可以看下面两个图,图一是两个EPWM同步的信号波形, 通道一是EPWM1模块产生的信号,通道二是EPWM2的波形

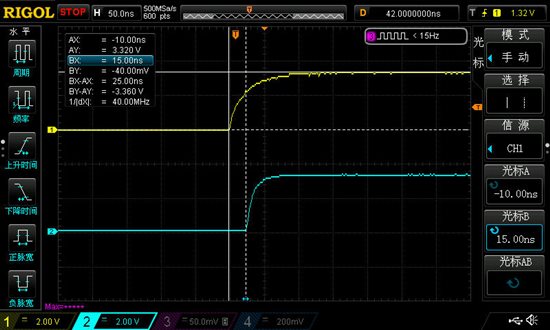

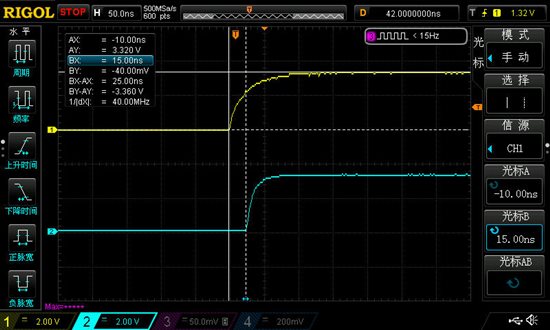

图二是波形展开后的情况,明显的EPWM2波形延迟于EPWM1的波形25ns(时钟80M),也就是正好差了俩个时钟周期,

因此,其实所谓的同步,并不是同步的。 25ns对于一个快速的系统来说 以及是很大很大的偏差了。

问题二:

从上第二图还可以发现,EPWM1的波形从低电平到达完全高电平的时间明显要比EPWM2长,我特地也对比了一下EPWM3/4,

发现其实就是EPWM1模块的上升时间要比其他EPWM模块长

上面两个问题 我无法解释,在datasheet 中貌似也没有解释过。

还有一个问题 问题三:

先抛开上面出现的延迟现象,我能不能仅仅同步EPWM1信号的EPWM2信号的下降沿?

也就是说,将信号一和信号二的下降沿放在一起 (试了很久,没有实现)

真心渴望、希望、盼望能有大神、朋友解释一下~

PS. 我用的是TMDSDOCK28335 TI自己的实验板,硬件上应该不会有什么问题

PPS. 主要程序如下:

EPwm1Regs.TBPRD = period; // Set timer period, PWM frequency = 1 / period

EPwm1Regs.TBPHS.all = 0; // Time-Base Phase Register

EPwm1Regs.TBCTR = 0; // Time-Base Counter Register

EPwm1Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; // Set Immediate load

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count-up mode: used for asymmetric PWM

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO ;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBPRD = period; // Set timer period, PWM frequency = 1 / period

EPwm2Regs.TBPHS.half.TBPHS = 0; // Time-Base Phase Register

EPwm2Regs.TBCTR = 0; // Time-Base Counter Register

EPwm2Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; // Set Immediate load

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count-up mode: used for asymmetric PWM

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

mangui zhang:

关于两路PWM不是同步 而是延迟2个clk 不知道有没有设置死区时间 死区是不是关掉了

关于上升快慢的问题 不是道两路PWM的负载是不是一样 如果没有接负载

那你的示波器两个通道的负载是不是设置一样?

示波器下降沿触发 抓不到一起吗

问题一:

在研究EPWM模块的时候,发现 其实所谓的时基同步,并不是同步的?

可以看下面两个图,图一是两个EPWM同步的信号波形, 通道一是EPWM1模块产生的信号,通道二是EPWM2的波形

图二是波形展开后的情况,明显的EPWM2波形延迟于EPWM1的波形25ns(时钟80M),也就是正好差了俩个时钟周期,

因此,其实所谓的同步,并不是同步的。 25ns对于一个快速的系统来说 以及是很大很大的偏差了。

问题二:

从上第二图还可以发现,EPWM1的波形从低电平到达完全高电平的时间明显要比EPWM2长,我特地也对比了一下EPWM3/4,

发现其实就是EPWM1模块的上升时间要比其他EPWM模块长

上面两个问题 我无法解释,在datasheet 中貌似也没有解释过。

还有一个问题 问题三:

先抛开上面出现的延迟现象,我能不能仅仅同步EPWM1信号的EPWM2信号的下降沿?

也就是说,将信号一和信号二的下降沿放在一起 (试了很久,没有实现)

真心渴望、希望、盼望能有大神、朋友解释一下~

PS. 我用的是TMDSDOCK28335 TI自己的实验板,硬件上应该不会有什么问题

PPS. 主要程序如下:

EPwm1Regs.TBPRD = period; // Set timer period, PWM frequency = 1 / period

EPwm1Regs.TBPHS.all = 0; // Time-Base Phase Register

EPwm1Regs.TBCTR = 0; // Time-Base Counter Register

EPwm1Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; // Set Immediate load

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count-up mode: used for asymmetric PWM

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO ;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBPRD = period; // Set timer period, PWM frequency = 1 / period

EPwm2Regs.TBPHS.half.TBPHS = 0; // Time-Base Phase Register

EPwm2Regs.TBCTR = 0; // Time-Base Counter Register

EPwm2Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; // Set Immediate load

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count-up mode: used for asymmetric PWM

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

Yang Xu2:

回复 mangui zhang:

① 死区是关掉了的 ② 空载的,示波器通道的负载设置是指? 两个探头完全一样,并且我也互换过通道测EPWM1和EPWM2 效果还是一样 ② 关于第三个问题可能是我没有说清楚,我的意思是: 现在说的同步是指上升沿同时出现,我想要得到的目标是,EPWM1高电平的下降沿出现的时候,DSP能实现EPWM2的下降沿也同时出现 这个问题虽然可以用其他方式解决,不知道能否仅仅通过配置同步信号的选取来完成这个任务。

TI中文支持网

TI中文支持网