28377中断嵌套可以嵌套几层

28377可以通过软件实现中断嵌套,即正在执行的低级别中断可以被已经来临的高级别中断打断,但他嵌套的层数应该受

28377可以通过软件实现中断嵌套,即正在执行的低级别中断可以被已经来临的高级别中断打断,但他嵌套的层数应该受

数据线D11与外部时钟输出XCLKOUT需要同时使用,但是他们两者是复用关系,需要如何解决?能否只用高16位数

如题,我尝试将DMA的目的地址设为DAC的输入地址,发现无法写入DAC的输入寄存器?器件支持该功能? 另外,A

在数据手册“Power Sequencing”部分没有看到内核VDD及VDDIO, V

如果不使用默认的SCIboot引脚,如何升级 使用c2prog或者serial_flash_programme

在F28377D中,如何将某一GPIO口设置到由CPU2控制?通过什么寄存器?还是说直接能控制?比如说通过CP

在F28377D中FIFO中,可否设置两个中断,也就是说使能FIFO功能,接收字节达到FIFO设置深度后会产生

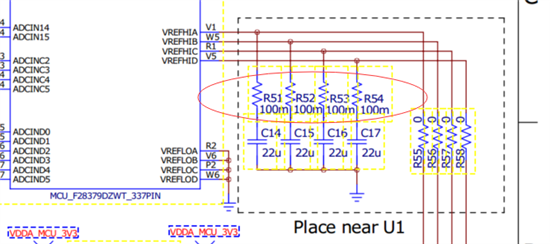

对于F2837X的controlCARD的原理图ADC参考电压滤波处有疑问,为什么要串一个电阻再接一个电容到地

在cpu2配置ipc0-3中断后,在cpu1设置IpcRegs.IPCSET.bit.IPC0 = 1;后,为

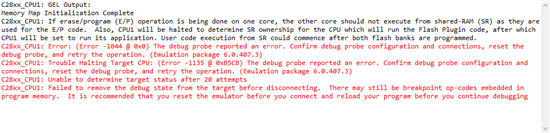

1,问题一 (RAM烧写情况下) 买了一块开发板(试过了程序没问题)。自制板子调试中,调用InitSysPll