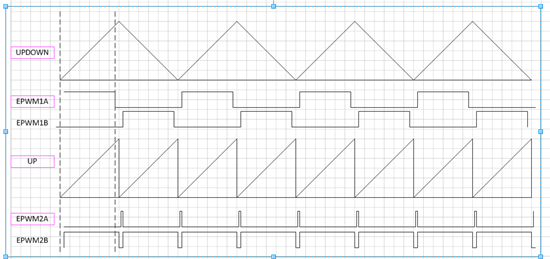

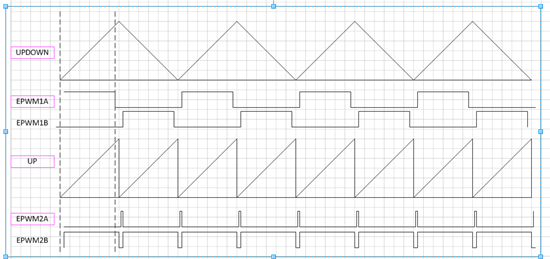

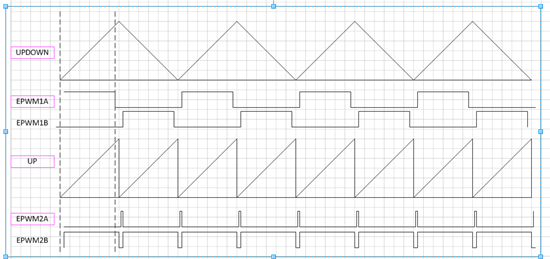

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

囧:

你现在的代码是不是只是EPWM2的?

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

bad:

回复 囧:

对的 这段代码是PWM_PSFB_PCMC_Cnf.c中的一部分

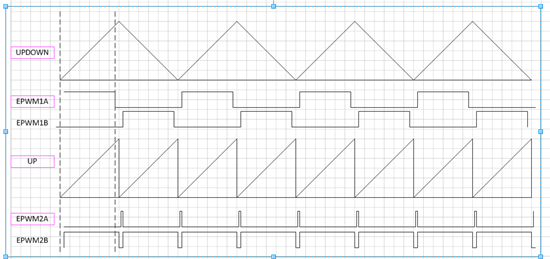

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

bad:

回复 囧:

为CMPA比TBPRD大,就没有输出?确定吗?

在ISR中,这样的语句很多啊:

MOV @_EPwm2Regs.CMPA.half.CMPA, AH MOV @_EPwm2Regs.CMPB, #(PWM_PRD+10)

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

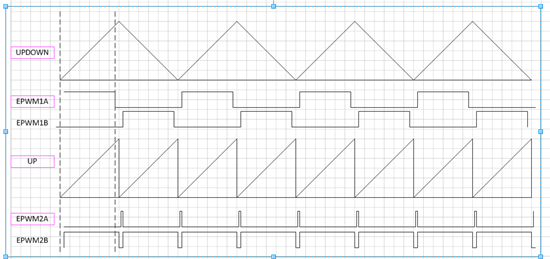

囧:

回复 bad:

TBCTR计数到TBPRD就清零了,那怎么可能匹配到CMPA?

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

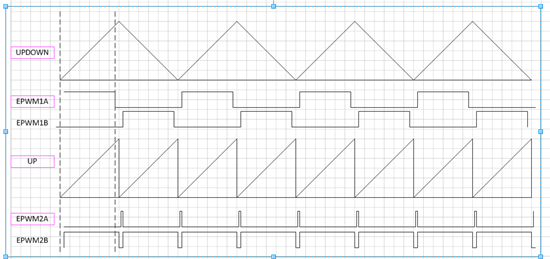

bad:

回复 囧:

好的,我再看看

下面是epwm的设置,我画了一个图,麻烦看看是不是这样,我自己感觉不是很正确

//Time Base SubModule Register

(*ePWM[n+1]).TBCTL.bit.PRDLD = TB_SHADOW; //Load from its Shadow Register

(*ePWM[n+1]).TBPRD = period-1;

(*ePWM[n+1]).TBPHS.half.TBPHS = 0; (*ePWM[n+1]).TBCTR = 0;

(*ePWM[n+1]).TBCTL.bit.CTRMODE = TB_COUNT_UP;

(*ePWM[n+1]).TBCTL.bit.PHSEN = TB_ENABLE;

(*ePWM[n+1]).TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync "flow through" mode

(*ePWM[n+1]).TBCTL.bit.HSPCLKDIV = TB_DIV1;

(*ePWM[n+1]).TBCTL.bit.CLKDIV = TB_DIV1;

// Counter compare submodule registers

(*ePWM[n+1]).CMPA.half.CMPA = period + 10; // Initial value (*ePWM[n+1]).CMPB = 20; // Initial value (*ePWM[n+1]).CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = Zero:TBCTR = Ox0000

(*ePWM[n+1]).CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Shadow mode

(*ePWM[n+1]).CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

(*ePWM[n+1]).CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Action Qualifier SubModule Registers

(*ePWM[n+1]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n+1]).AQCTLA.bit.CBU = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n+1]).AQCTLA.bit.PRD = AQ_CLEAR;

(*ePWM[n+1]).AQCTLB.bit.CBU = AQ_SET; (*ePWM[n+1]).AQCTLB.bit.CAU = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.ZRO = AQ_CLEAR; (*ePWM[n+1]).AQCTLB.bit.PRD = AQ_CLEAR;

bad:

回复 bad:

SPRUGE9E的43页有比较详细的说明

TI中文支持网

TI中文支持网