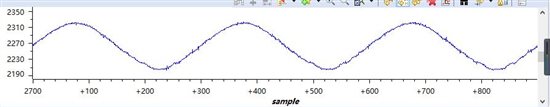

28335epwm产生中断,设置的脉冲10KHz。产生脉冲是100us,中断周期为什么是2.5ms。为什么不是100us哪?哪设置错了???

Terry Deng:

那你要看看中断的来源是设置到哪个地方

28335epwm产生中断,设置的脉冲10KHz。产生脉冲是100us,中断周期为什么是2.5ms。为什么不是100us哪?哪设置错了???

rui guo3:

回复 Terry Deng:

我是采用epwm1产生的中断。。是不是哪设置错误了?

EALLOW; PieVectTable.EPWM1_INT = &epwm1_isr; EDIS;

EALLOW; SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; EDIS;

// Enable CNT_zero interrupt using EPWM1 Time-base EPwm1Regs.ETPS.all=0x0000; EPwm1Regs.ETSEL.bit.INTEN = 1; // Enable EPWM1INT generation EPwm1Regs.ETSEL.bit.INTSEL = 1; // Enable interrupt CNT_zero event EPwm1Regs.ETPS.bit.INTPRD = 1; // EPwm1Regs.ETPS.bit.INTCNT=3; EPwm1Regs.ETCLR.bit.INT = 1; // Enable more interrupts

void InitEPwm1() { //时基模块TB设置 //时基周期寄存器 EPwm1Regs.TBPRD = PRD; // 设置周期 //时基相位寄存器 EPwm1Regs.TBPHS.half.TBPHS=0x0000; //phase is 0 //时基状态寄存器 EPwm1Regs.TBSTS.all=0x0000; //时基计数寄存器 EPwm1Regs.TBCTR = 0x0000; // Clear conuter //时基控制寄存器 EPwm1Regs.TBCTL.bit.SWFSYNC=0; EPwm1Regs.TBCTL.bit.CTRMODE = 0x2; //增减计数模式 EPwm1Regs.TBCTL.bit.PHSEN = 0;//TB_DISABLE; // Disable phase loading EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0; // Clock ratio to SYSCLKOUT /1 EPwm1Regs.TBCTL.bit.CLKDIV = 0; //TBCLK=SYSCLKOUT/(HSPCLKDIV*CLKDIV)=150MHz EPwm1Regs.TBCTL.bit.PRDLD = 1; //The period register (TBPRD) is loaded from its shadow register// when the time-base counter,TBCTR, is equal to zero EPwm1Regs.TBCTL.bit.SYNCOSEL = 3;//TB_CTR_ZERO; // Sync down-stream module,同步输出选择设定 EPwm1Regs.TBCTL.bit.FREE_SOFT=1; EPwm1Regs.TBCTL.bit.PHSDIR=0; EPwm1Regs.TBCTL.bit.SWFSYNC=1;//比较计数模块CC设置 //计数比较控制寄存 EPwm1Regs.CMPCTL.all=0x0000; EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; //动作模块AQ设置 //ePWMA动作模块控制寄存器 EPwm1Regs.AQCTLA.all=0x0000; EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on event A, up count EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR; // Clear PWM1A on event A, down count

//死区模块DB设置 //死区控制寄存器 EPwm1Regs.DBCTL.all=0x0000; EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL; // enable Dead-band module EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; // Active low complementary (ALC) mode. EPWMxA is inverted. EPwm1Regs.DBCTL.bit.OUT_MODE = DB_ACTV_LO; //低电平有效,互补输出。 //死区下降沿延时寄存器 EPwm1Regs.DBFED = 200; // FED = 200 TBCLKs //死区上升沿延时寄存器 EPwm1Regs.DBRED = 200; // RED = 200 TBCLKs }

IER |= M_INT3; //EPWM1的中断

PieCtrlRegs.PIEIER3.bit.INTx1 = 1; EINT; //开中断 ERTM;

28335epwm产生中断,设置的脉冲10KHz。产生脉冲是100us,中断周期为什么是2.5ms。为什么不是100us哪?哪设置错了???

rui guo3:

回复 rui guo3:

解决了,原来epwmA中断中加了一个2毫秒的延时,所以导致上面问题。。。

TI中文支持网

TI中文支持网