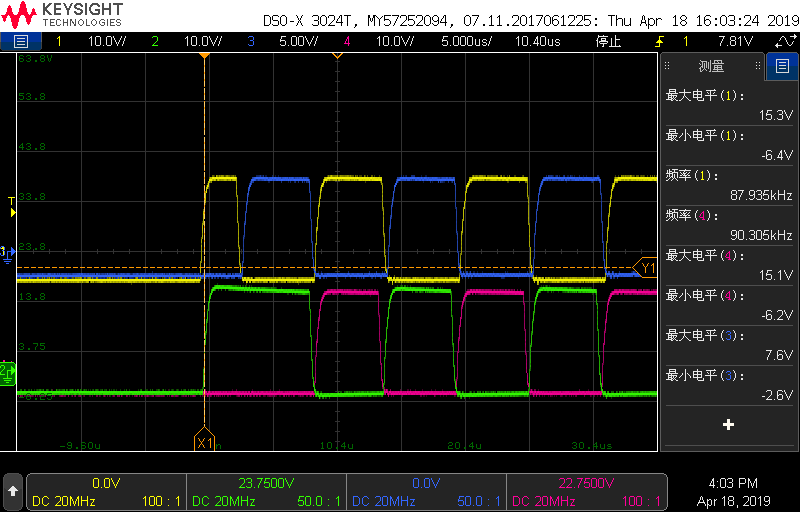

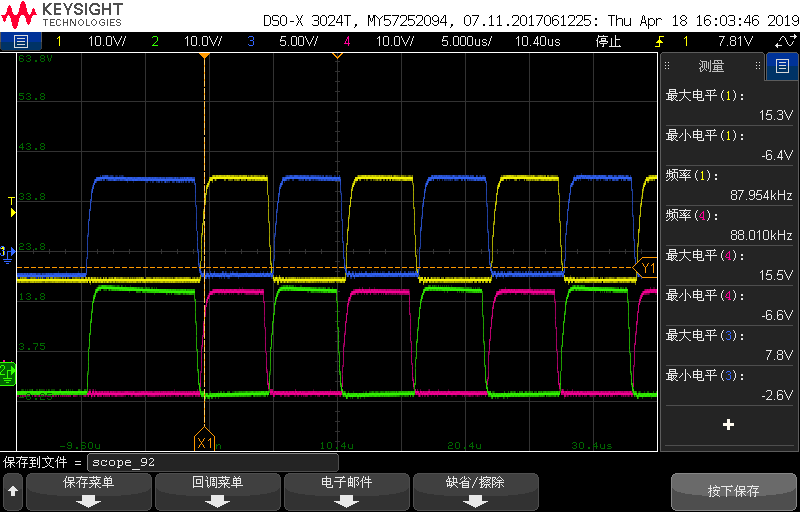

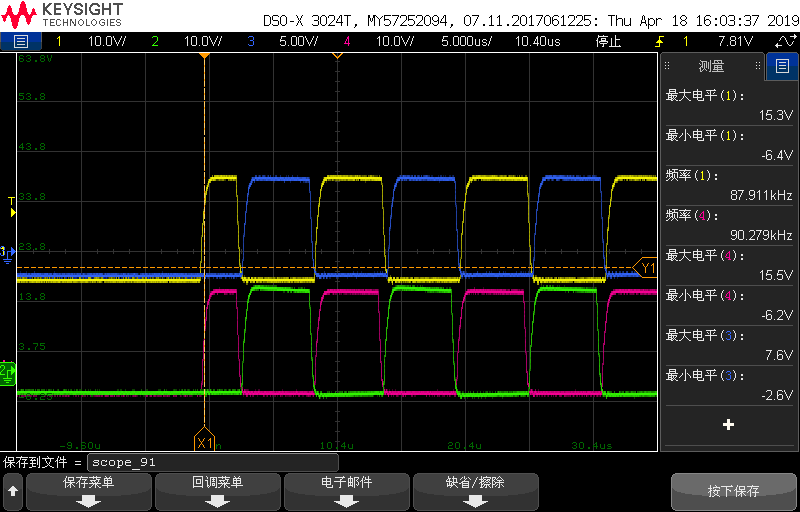

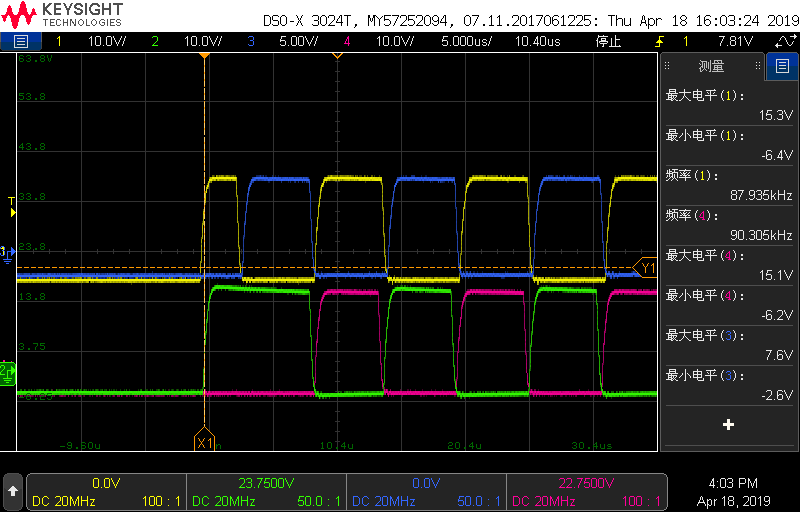

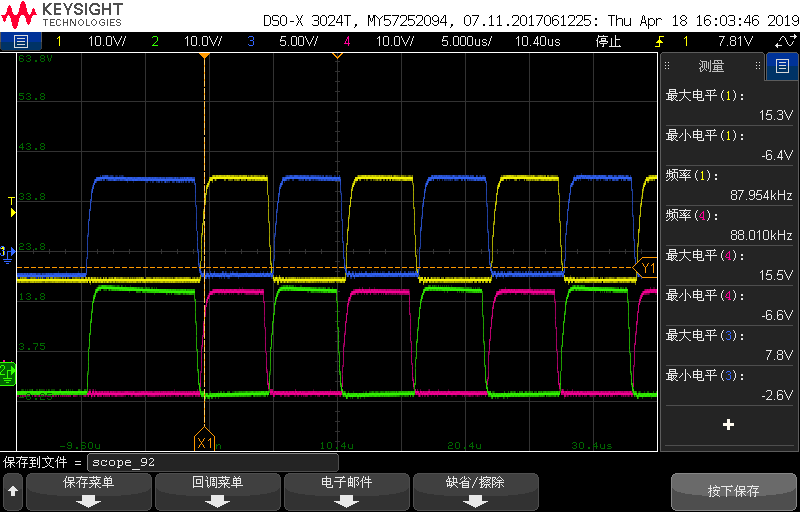

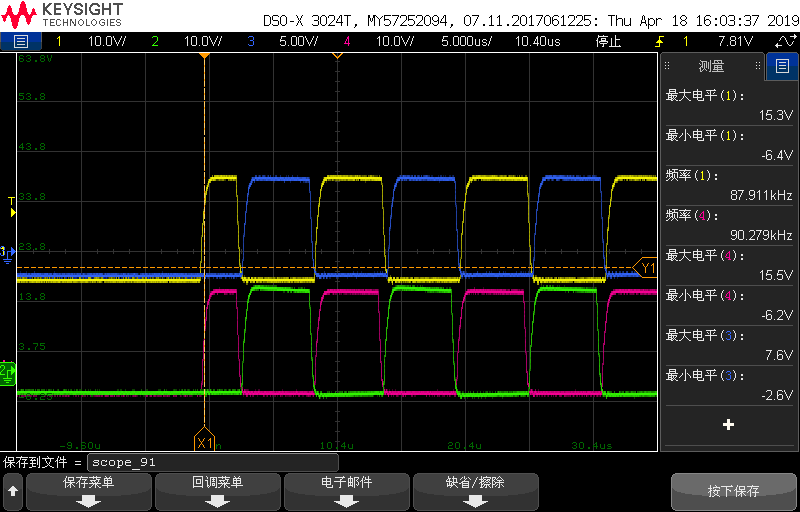

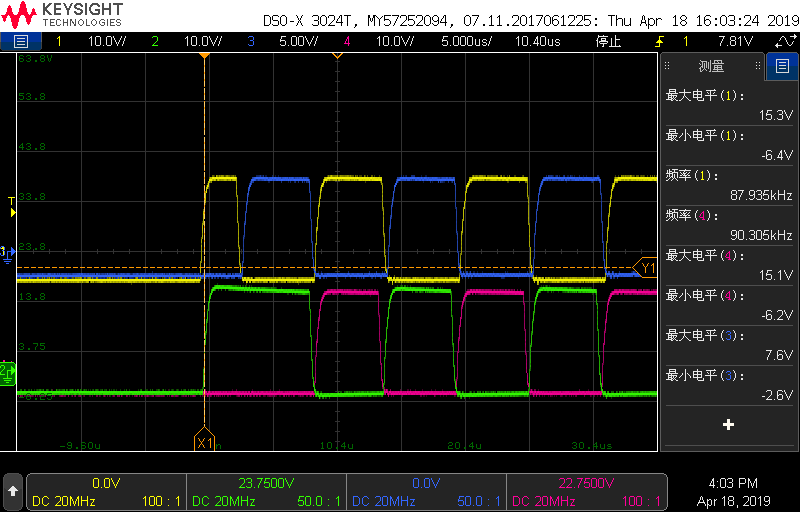

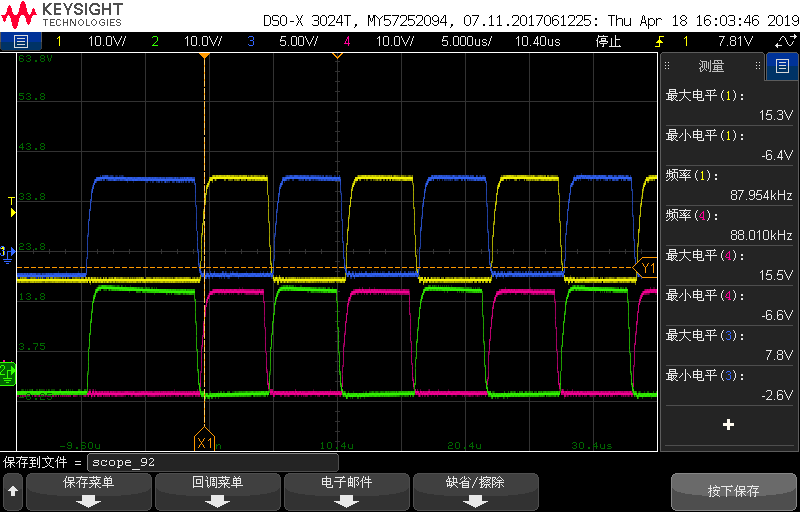

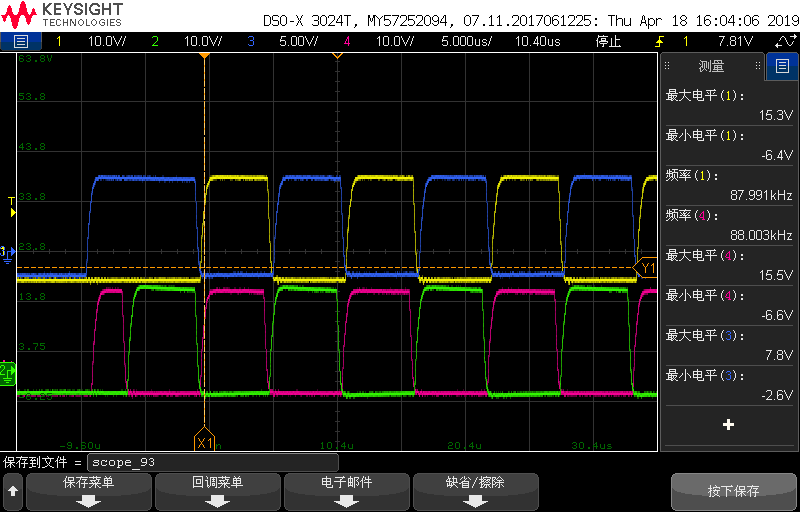

最近在测试移相全桥的pwm,发现pwm的开启的时刻,第一个周期会出现不固定的脉冲丢失问题,如下图所示,

上面3图的问题都是随机出现。

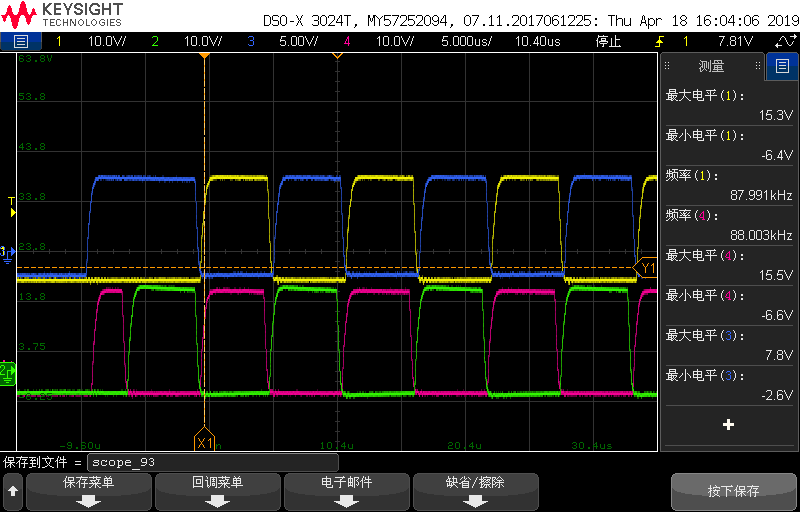

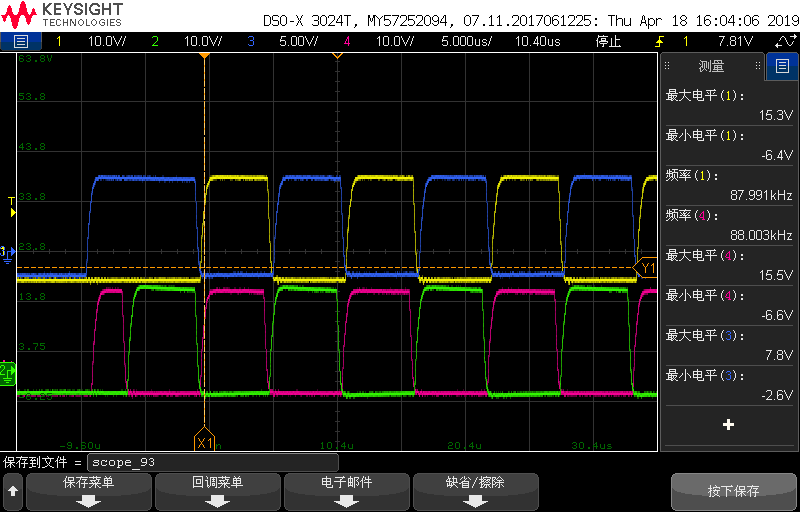

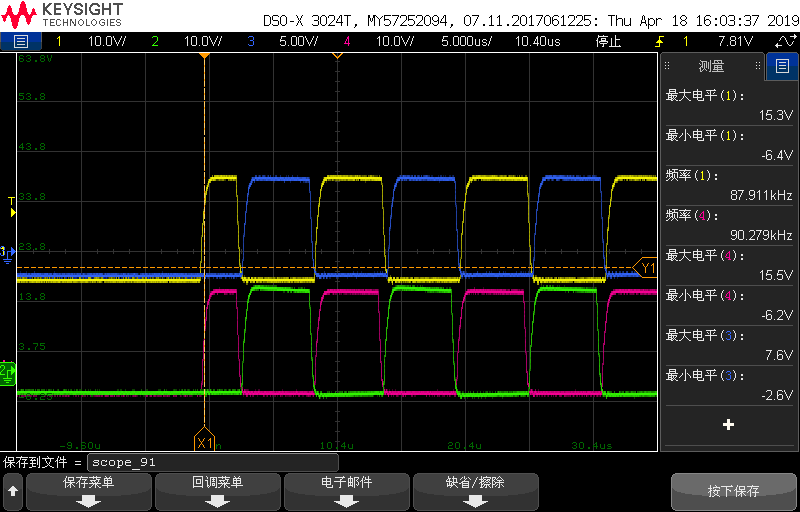

下面这个图是正常的波形,但是只是偶尔才会出现

想请教TI员工,这是什么原因导致的?

另外附上代码:

//

// InitEPwm1Example – Initialize EPWM1 configuration

//

void InitEPwm1Example()

{

EPwm1Regs.TBPRD = 1000; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //sync Time-base counter = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Setup compare

//

EPwm1Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low PWMs – Setup Deadband

//

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBRED.bit.DBRED = EPWM1_MIN_DB;

EPwm1Regs.DBFED.bit.DBFED = EPWM1_MIN_DB;

Setup_PWM1_Trip();

}

//

// InitEPwm2Example – Initialize EPWM2 configuration

//

void InitEPwm2Example()

{

EPwm2Regs.TBPRD = 1000; // Set timer period

EPwm2Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // Slow just to observe on

// the scope

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //sync Time-base counter = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

//

// Setup compare

//

EPwm2Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM2A on Zero

EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM2A on Zero

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low complementary PWMs – setup the deadband

//

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm2Regs.DBRED.bit.DBRED = EPWM2_MIN_DB;

EPwm2Regs.DBFED.bit.DBFED = EPWM2_MIN_DB;

Setup_PWM2_Trip();

}

开启pwm调用 EPwm1Regs.TZCLR.bit.OST = 0x01;

Annie Liu:

为更加有效地解决您的问题,我们建议您将问题发布在E2E英文技术论坛上https://e2e.ti.com/support/microcontrollers/c2000/f/171,将由资深的工程师为您提供帮助。我们的E2E英文社区有TI专家进行回复,并得到全球各地工程师的支持,分享他们的知识和经验。

最近在测试移相全桥的pwm,发现pwm的开启的时刻,第一个周期会出现不固定的脉冲丢失问题,如下图所示,

上面3图的问题都是随机出现。

下面这个图是正常的波形,但是只是偶尔才会出现

想请教TI员工,这是什么原因导致的?

另外附上代码:

//

// InitEPwm1Example – Initialize EPWM1 configuration

//

void InitEPwm1Example()

{

EPwm1Regs.TBPRD = 1000; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //sync Time-base counter = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Setup compare

//

EPwm1Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low PWMs – Setup Deadband

//

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBRED.bit.DBRED = EPWM1_MIN_DB;

EPwm1Regs.DBFED.bit.DBFED = EPWM1_MIN_DB;

Setup_PWM1_Trip();

}

//

// InitEPwm2Example – Initialize EPWM2 configuration

//

void InitEPwm2Example()

{

EPwm2Regs.TBPRD = 1000; // Set timer period

EPwm2Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // Slow just to observe on

// the scope

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //sync Time-base counter = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

//

// Setup compare

//

EPwm2Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM2A on Zero

EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM2A on Zero

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low complementary PWMs – setup the deadband

//

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm2Regs.DBRED.bit.DBRED = EPWM2_MIN_DB;

EPwm2Regs.DBFED.bit.DBFED = EPWM2_MIN_DB;

Setup_PWM2_Trip();

}

开启pwm调用 EPwm1Regs.TZCLR.bit.OST = 0x01;

mangui zhang:这种只丢失一个的比较难定位是不是和你的理解有关啊其实工作正常

最近在测试移相全桥的pwm,发现pwm的开启的时刻,第一个周期会出现不固定的脉冲丢失问题,如下图所示,

上面3图的问题都是随机出现。

下面这个图是正常的波形,但是只是偶尔才会出现

想请教TI员工,这是什么原因导致的?

另外附上代码:

//

// InitEPwm1Example – Initialize EPWM1 configuration

//

void InitEPwm1Example()

{

EPwm1Regs.TBPRD = 1000; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //sync Time-base counter = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//

// Setup compare

//

EPwm1Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on Zero

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM1A on Zero

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low PWMs – Setup Deadband

//

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBRED.bit.DBRED = EPWM1_MIN_DB;

EPwm1Regs.DBFED.bit.DBFED = EPWM1_MIN_DB;

Setup_PWM1_Trip();

}

//

// InitEPwm2Example – Initialize EPWM2 configuration

//

void InitEPwm2Example()

{

EPwm2Regs.TBPRD = 1000; // Set timer period

EPwm2Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

//

// Setup TBCLK

//

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // Slow just to observe on

// the scope

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //sync Time-base counter = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero

//

// Setup compare

//

EPwm2Regs.CMPA.bit.CMPA = 500;

//

// Set actions

//

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM2A on Zero

EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Set PWM2A on Zero

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// Active Low complementary PWMs – setup the deadband

//

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm2Regs.DBRED.bit.DBRED = EPWM2_MIN_DB;

EPwm2Regs.DBFED.bit.DBFED = EPWM2_MIN_DB;

Setup_PWM2_Trip();

}

开启pwm调用 EPwm1Regs.TZCLR.bit.OST = 0x01;

user4817944:

回复 mangui zhang:

但是我如果把CPU定时器关闭掉,这个就不会出现了。。。

问题是,定时器中断里只有十几个计数值增加的操作,按理说应该不会影响吧,就算有影响,为什么只有开启的时刻才会出现?

TI中文支持网

TI中文支持网

![TMS320F280039C: CBC逐波限流模式下DCBCTL[EVT2LATSEL]寄存器这一位的作用-TI中文支持网](https://www.ti2k.com/wp-content/uploads/ti2k/DeyiSupport_C2000__AE5FE14FFE5647725F00_20241022143501.jpg)