dsp2812的ADC中有最大转换通道寄存器,而dsp28035中没有,当我只想采样3个通道时,dsp28035怎么设置呢?而且它的寄存器的默认值大多为0,如果不设置,也不符合我的期望。

mangui zhang:

每一路的SOC可以自由选择采样通道 以前的可能排好序后顺序去转换

dsp2812的ADC中有最大转换通道寄存器,而dsp28035中没有,当我只想采样3个通道时,dsp28035怎么设置呢?而且它的寄存器的默认值大多为0,如果不设置,也不符合我的期望。

Susan Yang:SOC可以理解为一个内部事件,这个事件决定了转换和采样的优先级,而这个事件可以独立配置到任意外部ADC引脚,以及配置自己的采样窗宽度,和被触发采样的触发源。所以会相对F28335的顺序触发采样灵活,也就是您可以理解为每个采样通道都可以通过SOC的配置变成任意优先级。并且通过不同的触发源配置可以控制不同的采样周期。

转 e2echina.ti.com/…/114875

您可以设置 AdcRegs.ADCSOCxCTL.bit.CHSEL

dsp2812的ADC中有最大转换通道寄存器,而dsp28035中没有,当我只想采样3个通道时,dsp28035怎么设置呢?而且它的寄存器的默认值大多为0,如果不设置,也不符合我的期望。

user5860441:

回复 Susan Yang:

AdcRegs.ADCSOCxCTL.bit.CHSEL的默认值是0,现在我只想采样3个通道,AdcRegs.ADCSOC0CTL.bit.CHSEL = 0;AdcRegs.ADCSOC1CTL.bit.CHSEL = 1;AdcRegs.ADCSOC2CTL.bit.CHSEL =2;那其他AdcRegs.ADCSOCxCTL.bit.CHSEL是0,是不是也不适合?

我做了一个实验,通道选择,我只写了两句话,ADCSOC0CTL ADCSOC1CTL分别选了ADCINA0和ADCINA1,查看ADC结果寄存器,发现ADCRESULT0和ADCRESULT1有数据,其它的结果寄存器全是0,其它通道应该没有转换。但是还是不明白为什么?

dsp2812的ADC中有最大转换通道寄存器,而dsp28035中没有,当我只想采样3个通道时,dsp28035怎么设置呢?而且它的寄存器的默认值大多为0,如果不设置,也不符合我的期望。

Susan Yang:

回复 user5860441:

只想采样3个通道,您就只需设置 AdcRegs.ADCSOC0CTL.bit.CHSEL = 0;AdcRegs.ADCSOC1CTL.bit.CHSEL = 1;AdcRegs.ADCSOC2CTL.bit.CHSEL =2;那其他AdcRegs.ADCSOCxCTL.bit.CHSEL不需要您再去设置

关于您的实验,能给出详细代码吗?

dsp2812的ADC中有最大转换通道寄存器,而dsp28035中没有,当我只想采样3个通道时,dsp28035怎么设置呢?而且它的寄存器的默认值大多为0,如果不设置,也不符合我的期望。

user5860441:

回复 Susan Yang:

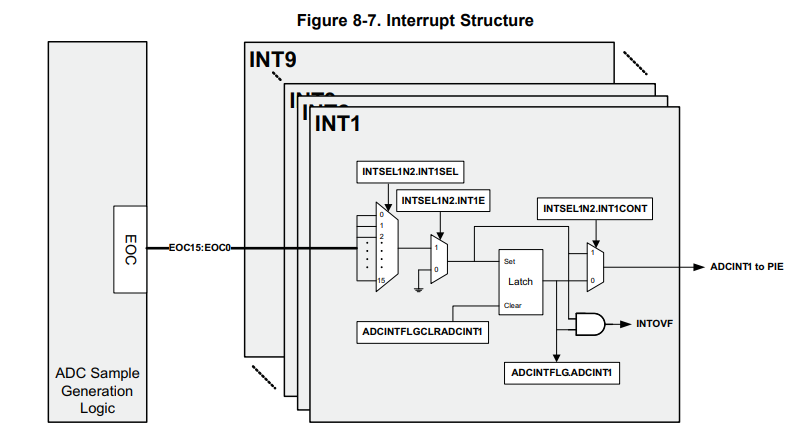

// Configure ADCEALLOW;AdcRegs.ADCCTL1.bit.INTPULSEPOS = 1; //ADCINT1 trips after AdcResults latch;1 在转换结束产生中断0 在转换开始产生中断AdcRegs.INTSEL1N2.bit.INT1E= 1; //Enabled ADCINT1 触发cla taskAdcRegs.INTSEL1N2.bit.INT1CONT= 0; //Disable ADCINT1 Continuous modeAdcRegs.INTSEL1N2.bit.INT1SEL = 0x01; //setup EOC1 to trigger ADCINT1 to fire

AdcRegs.ADCSOC0CTL.bit.CHSEL= 0; //set SOC0 channel select to ADCINA0AdcRegs.ADCSOC1CTL.bit.CHSEL= 1; //set SOC1 channel select to ADCINA1

/* AdcRegs.ADCSOC2CTL.bit.CHSEL= 2; //set SOC2 channel select to ADCINA2AdcRegs.ADCSOC3CTL.bit.CHSEL= 3; //set SOC3 channel select to ADCINA3AdcRegs.ADCSOC4CTL.bit.CHSEL= 4; //set SOC4 channel select to ADCINA4AdcRegs.ADCSOC5CTL.bit.CHSEL= 5; //set SOC5 channel select to ADCINA5AdcRegs.ADCSOC6CTL.bit.CHSEL= 6; //set SOC6 channel select to ADCINA6AdcRegs.ADCSOC7CTL.bit.CHSEL= 7; //set SOC7 channel select to ADCINA7AdcRegs.ADCSOC8CTL.bit.CHSEL= 8; //set SOC8 channel select to ADCINB0AdcRegs.ADCSOC9CTL.bit.CHSEL= 9; //set SOC9 channel select to ADCINB1AdcRegs.ADCSOC10CTL.bit.CHSEL= 10; //set SOC10 channel select to ADCINB2AdcRegs.ADCSOC11CTL.bit.CHSEL= 11; //set SOC11 channel select to ADCINB3AdcRegs.ADCSOC12CTL.bit.CHSEL= 12; //set SOC12 channel select to ADCINB4AdcRegs.ADCSOC13CTL.bit.CHSEL= 13; //set SOC13 channel select to ADCINB5AdcRegs.ADCSOC14CTL.bit.CHSEL= 14; //set SOC14 channel select to ADCINB6AdcRegs.ADCSOC15CTL.bit.CHSEL= 15; //set SOC15 channel select to ADCINB7

*/AdcRegs.ADCSOC0CTL.bit.TRIGSEL= 0x0B; //set ePWM4, ADCSOCA as the trigger sourceAdcRegs.ADCSOC1CTL.bit.TRIGSEL= 0x0B;

/* AdcRegs.ADCSOC2CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC3CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC4CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC5CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC6CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC7CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC8CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC9CTL.bit.TRIGSEL= 5;AdcRegs.ADCSOC10CTL.bit.TRIGSEL = 5;AdcRegs.ADCSOC11CTL.bit.TRIGSEL = 5;AdcRegs.ADCSOC12CTL.bit.TRIGSEL = 5;AdcRegs.ADCSOC13CTL.bit.TRIGSEL = 5;AdcRegs.ADCSOC14CTL.bit.TRIGSEL = 5;AdcRegs.ADCSOC15CTL.bit.TRIGSEL = 5;

*/AdcRegs.ADCSOC0CTL.bit.ACQPS= 9; //set SOC0 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC1CTL.bit.ACQPS= 9; //set SOC1 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)

/* AdcRegs.ADCSOC2CTL.bit.ACQPS= 9; //set SOC2 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC3CTL.bit.ACQPS= 9; //set SOC3 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC4CTL.bit.ACQPS= 9; //set SOC4 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC5CTL.bit.ACQPS= 9; //set SOC5 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC6CTL.bit.ACQPS= 9; //set SOC6 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC7CTL.bit.ACQPS= 9; //set SOC7 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC8CTL.bit.ACQPS= 9; //set SOC8 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC9CTL.bit.ACQPS= 9; //set SOC9 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC10CTL.bit.ACQPS= 9; //set SOC10 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC11CTL.bit.ACQPS= 9; //set SOC11 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC12CTL.bit.ACQPS= 9; //set SOC12 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC13CTL.bit.ACQPS= 9; //set SOC13 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC14CTL.bit.ACQPS= 9; //set SOC14 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)AdcRegs.ADCSOC15CTL.bit.ACQPS= 9; //set SOC15 S/H Window to 7 ADC Clock Cycles, (9 ACQPS plus 1)

*/AdcRegs.ADCINTSOCSEL1.bit.SOC0= 0;//No ADCINT will trigger SOCx. TRIGSEL field determines SOCx trigger.AdcRegs.ADCINTSOCSEL1.bit.SOC1= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC2= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC3= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC4= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC5= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC6= 0;AdcRegs.ADCINTSOCSEL1.bit.SOC7= 0;AdcRegs.ADCINTSOCSEL2.bit.SOC8= 0;AdcRegs.ADCINTSOCSEL2.bit.SOC9= 0;AdcRegs.ADCINTSOCSEL2.bit.SOC10 = 0;AdcRegs.ADCINTSOCSEL2.bit.SOC11 = 0;AdcRegs.ADCINTSOCSEL2.bit.SOC12 = 0;AdcRegs.ADCINTSOCSEL2.bit.SOC13 = 0;AdcRegs.ADCINTSOCSEL2.bit.SOC14 = 0;AdcRegs.ADCINTSOCSEL2.bit.SOC15 = 0;EDIS;

TI中文支持网

TI中文支持网