怎样使用28069的内部模拟比较器的输出,来产生ePWM模块的同步信号。

下面是我相关部分的代码:

比较器部分:

EALLOW;SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; //(*Device_cal)();AdcRegs.ADCCTL1.bit.ADCPWDN = 1;AdcRegs.ADCCTL1.bit.ADCBGPWD = 1;DELAY_US(1000);SysCtrlRegs.PCLKCR3.bit.COMP1ENCLK=1;AdcRegs.ADCCTL1.bit.VREFLOCONV=1;Comp1Regs.COMPCTL.bit.COMPDACEN = 1;//使能比较器Comp1Regs.COMPCTL.bit.SYNCSEL = 0;//异步输出Comp1Regs.COMPCTL.bit.QUALSEL = 0;//窗口滤波Comp1Regs.COMPCTL.bit.CMPINV = 0;//反转输出Comp1Regs.COMPCTL.bit.COMPSOURCE = 0;//comp1b(+)连接到内部DACComp1Regs.DACCTL.bit.DACSOURCE = 0;Comp1Regs.DACVAL.bit.DACVAL = 465;// 1.5VEDIS;

ePWM模块部分:

EALLOW;EPwm1Regs.TBPRD = 60000;// Set timer periodEPwm1Regs.TBPHS.all = 0;// Phase is 0EPwm1Regs.TBCTR = 0;// Setup TBCLKEPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;// Count upEPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE;// when sync comes, TBCTR=TBPHSEPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // These bits select the source of the EPWMxSYNCO signal. 0 means EPWMxSYNC// TB_SYNC_IN=0EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0 ;// Clock ratio to SYSCLKOUTEPwm1Regs.TBCTL.bit.CLKDIV = 0;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;// Load registers every ZEROEPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;// Setup compareEPwm1Regs.CMPA.half.CMPA = 50; // 40/8*(10^7) = 500nsEPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;// Set PWM1A on CAU当CTR=0时,强制EPWM1A输出高电平EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//当CTR=CMPA且计数器CTR增计数时,强制EPWM1A输出低电平EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module 用于EPWMxA输出上升沿延迟及EPWMxB输出下降沿延迟的死区均被使能。// 延迟输入信号由DBCTL[IN_MODE]字段决定,默认EPWMxA作为下降沿与上升沿延迟的输入源。EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;// Active Hi complementary 高电平互补(AHC)模式:EPWMxB反向。EPwm1Regs.DBRED = 4;// 上升沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DBFED = 14;// 下降沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT;// DCAH = Comparator 1 output DCAH的电平高低由比较器1的输出决定EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI;EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1;//EPwm1Regs.DCACTL.bit.EVT1SYNCE = 1;//EDIS;

我将COMP1比较器的反相输入端配置为DAC输入,正相输入端为外部模拟引脚输入。当我在正相输入一个高电平的时候,没有产生ePWM1的同步信号。

我想问一下,

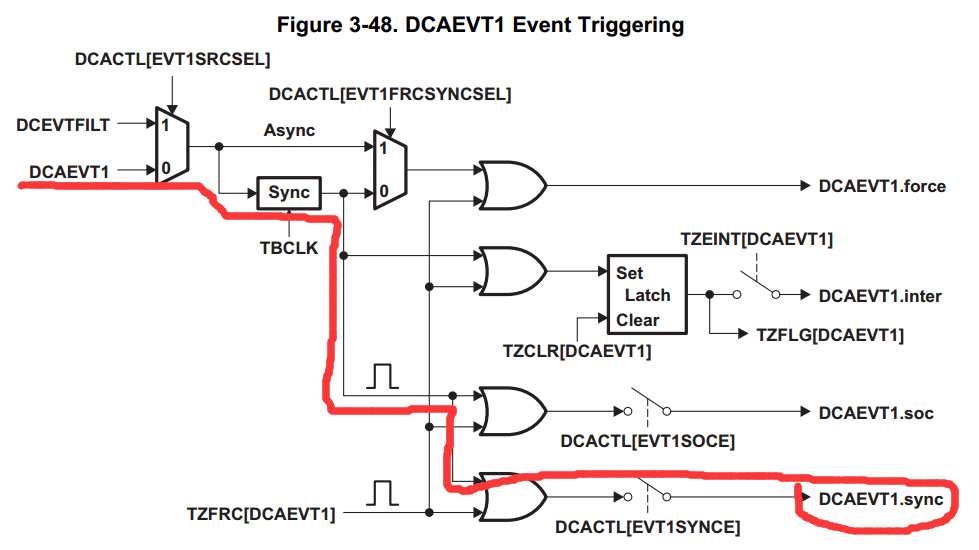

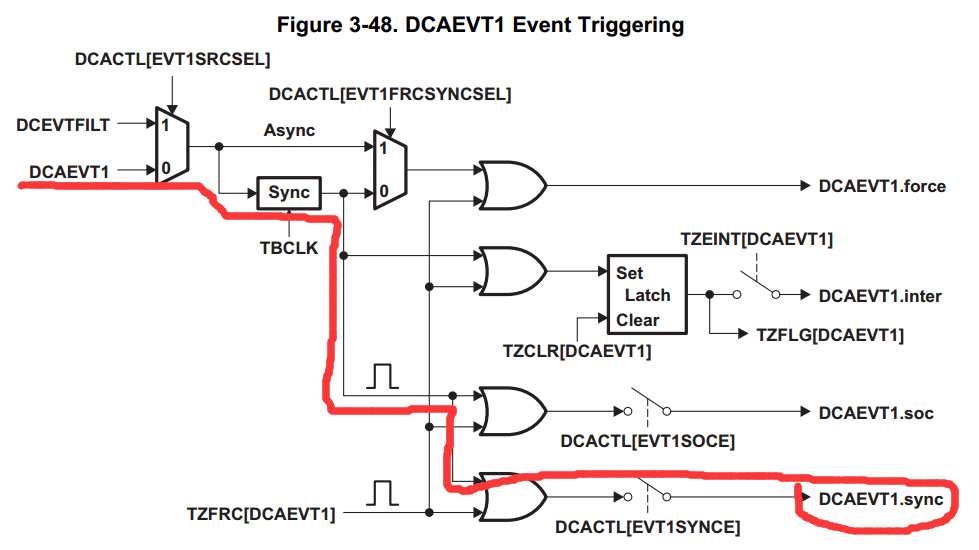

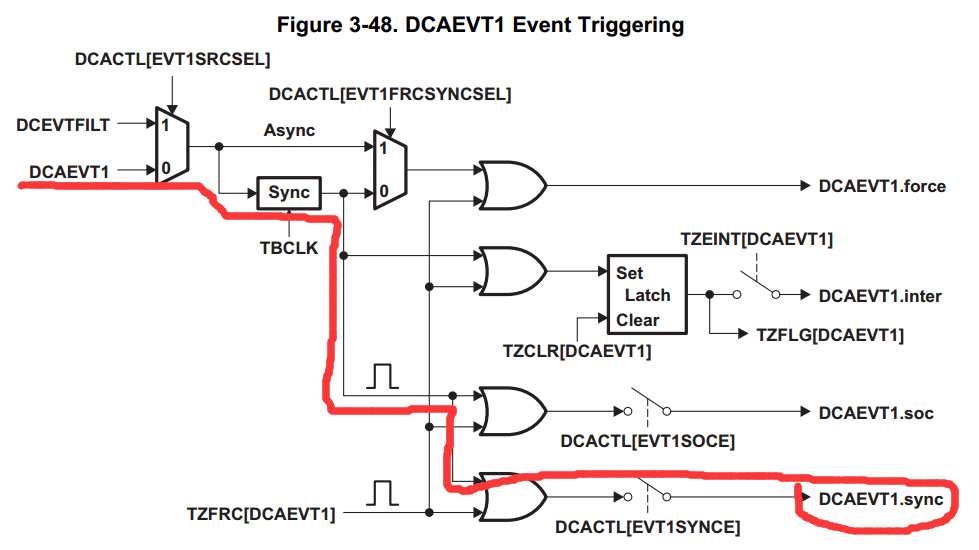

1、ePWM的DC模块产生的DCAEVT1.sync 信号是CBC还是OSHT的?

2、比较器输出 怎样触发DCAEVT1.sync 这个信号?我上面的配置方法是正确的吗?

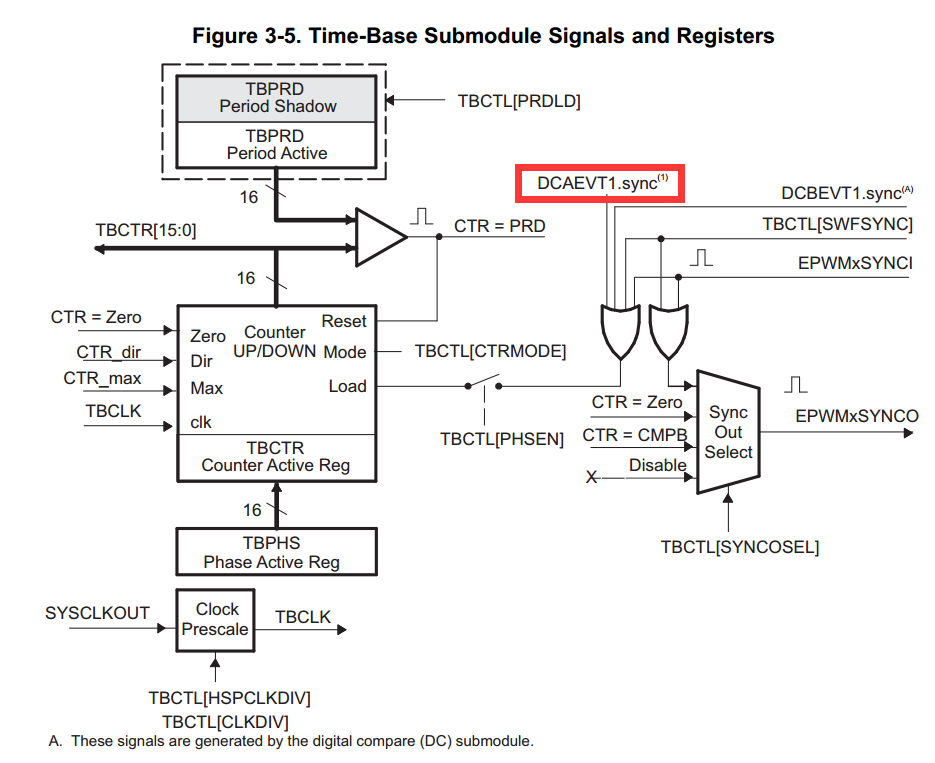

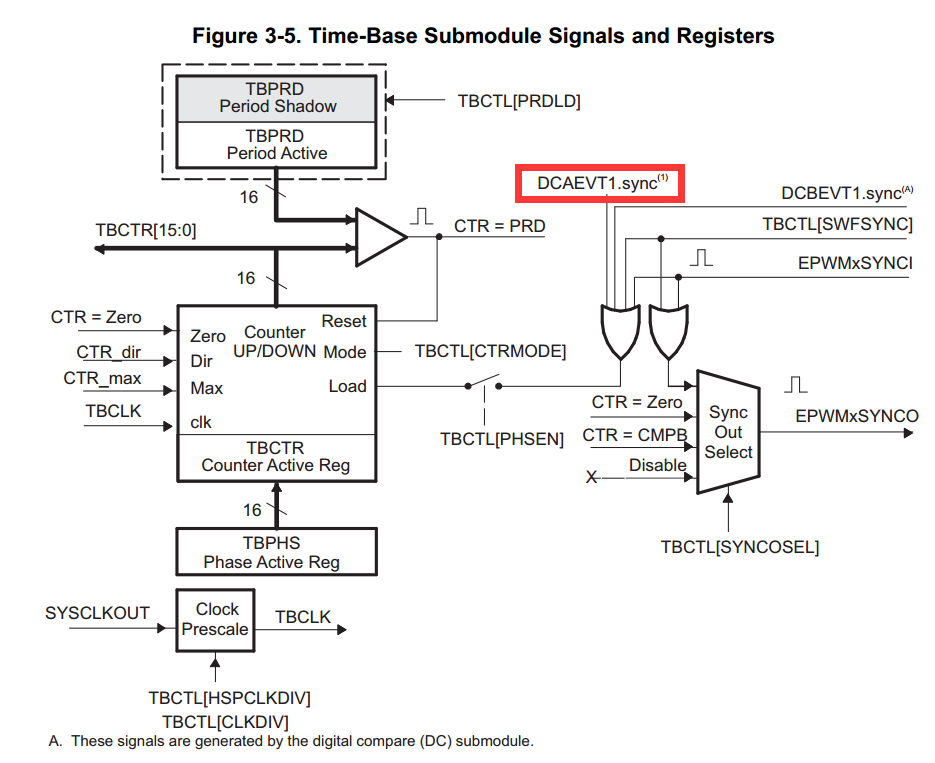

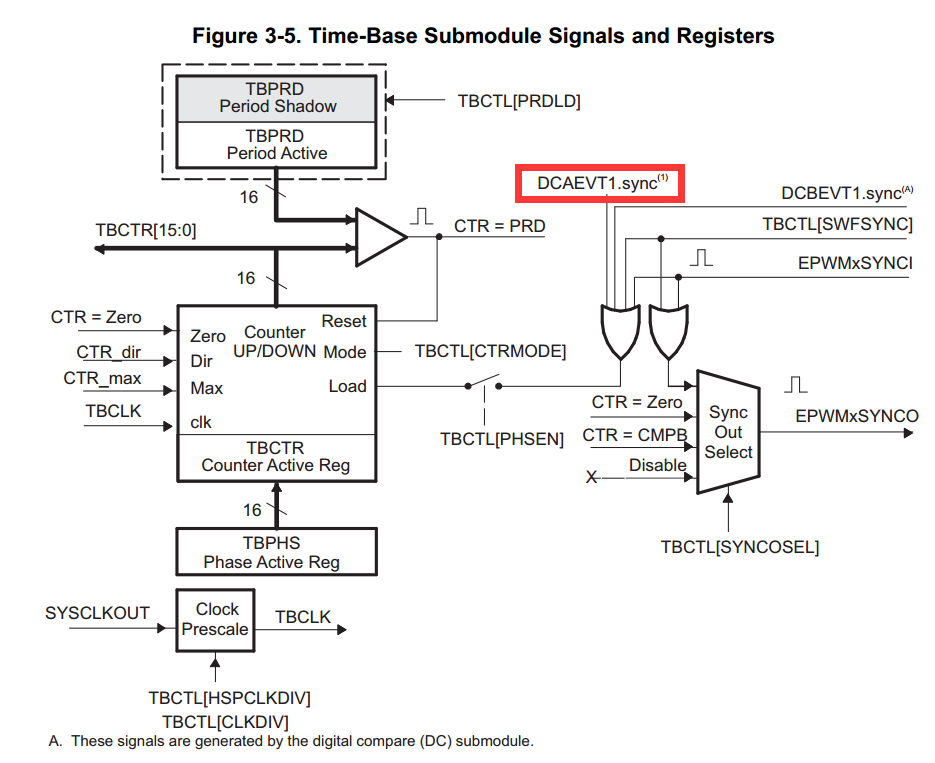

3、如第二个图所示,DCAEVT1.sync不需要其他配置,只要产生了,就可以让ePWM同步吗?

Brian Wang0:比较器模块与adc共用内部供电,因此如果要使用比较器,即使不使用ADC也不能Power off

可以参考例程Example_2806xEPwmDCEventTripComp 的配置方法

怎样使用28069的内部模拟比较器的输出,来产生ePWM模块的同步信号。

下面是我相关部分的代码:

比较器部分:

EALLOW;SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; //(*Device_cal)();AdcRegs.ADCCTL1.bit.ADCPWDN = 1;AdcRegs.ADCCTL1.bit.ADCBGPWD = 1;DELAY_US(1000);SysCtrlRegs.PCLKCR3.bit.COMP1ENCLK=1;AdcRegs.ADCCTL1.bit.VREFLOCONV=1;Comp1Regs.COMPCTL.bit.COMPDACEN = 1;//使能比较器Comp1Regs.COMPCTL.bit.SYNCSEL = 0;//异步输出Comp1Regs.COMPCTL.bit.QUALSEL = 0;//窗口滤波Comp1Regs.COMPCTL.bit.CMPINV = 0;//反转输出Comp1Regs.COMPCTL.bit.COMPSOURCE = 0;//comp1b(+)连接到内部DACComp1Regs.DACCTL.bit.DACSOURCE = 0;Comp1Regs.DACVAL.bit.DACVAL = 465;// 1.5VEDIS;

ePWM模块部分:

EALLOW;EPwm1Regs.TBPRD = 60000;// Set timer periodEPwm1Regs.TBPHS.all = 0;// Phase is 0EPwm1Regs.TBCTR = 0;// Setup TBCLKEPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;// Count upEPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE;// when sync comes, TBCTR=TBPHSEPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // These bits select the source of the EPWMxSYNCO signal. 0 means EPWMxSYNC// TB_SYNC_IN=0EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0 ;// Clock ratio to SYSCLKOUTEPwm1Regs.TBCTL.bit.CLKDIV = 0;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;// Load registers every ZEROEPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;// Setup compareEPwm1Regs.CMPA.half.CMPA = 50; // 40/8*(10^7) = 500nsEPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;// Set PWM1A on CAU当CTR=0时,强制EPWM1A输出高电平EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//当CTR=CMPA且计数器CTR增计数时,强制EPWM1A输出低电平EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module 用于EPWMxA输出上升沿延迟及EPWMxB输出下降沿延迟的死区均被使能。// 延迟输入信号由DBCTL[IN_MODE]字段决定,默认EPWMxA作为下降沿与上升沿延迟的输入源。EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;// Active Hi complementary 高电平互补(AHC)模式:EPWMxB反向。EPwm1Regs.DBRED = 4;// 上升沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DBFED = 14;// 下降沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT;// DCAH = Comparator 1 output DCAH的电平高低由比较器1的输出决定EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI;EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1;//EPwm1Regs.DCACTL.bit.EVT1SYNCE = 1;//EDIS;

我将COMP1比较器的反相输入端配置为DAC输入,正相输入端为外部模拟引脚输入。当我在正相输入一个高电平的时候,没有产生ePWM1的同步信号。

我想问一下,

1、ePWM的DC模块产生的DCAEVT1.sync 信号是CBC还是OSHT的?

2、比较器输出 怎样触发DCAEVT1.sync 这个信号?我上面的配置方法是正确的吗?

3、如第二个图所示,DCAEVT1.sync不需要其他配置,只要产生了,就可以让ePWM同步吗?

tao lee36:

回复 Brian Wang0:

我已经在配置比较器寄存器的时候把ADC POWER UP了,代码如下

AdcRegs.ADCCTL1.bit.ADCPWDN = 1; AdcRegs.ADCCTL1.bit.ADCBGPWD = 1;

我的的代码经过测试,比较器已经可以正确输出了,我的问题主要集中在 如何使用比较器的输出来同步ePWM。

怎样使用28069的内部模拟比较器的输出,来产生ePWM模块的同步信号。

下面是我相关部分的代码:

比较器部分:

EALLOW;SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; //(*Device_cal)();AdcRegs.ADCCTL1.bit.ADCPWDN = 1;AdcRegs.ADCCTL1.bit.ADCBGPWD = 1;DELAY_US(1000);SysCtrlRegs.PCLKCR3.bit.COMP1ENCLK=1;AdcRegs.ADCCTL1.bit.VREFLOCONV=1;Comp1Regs.COMPCTL.bit.COMPDACEN = 1;//使能比较器Comp1Regs.COMPCTL.bit.SYNCSEL = 0;//异步输出Comp1Regs.COMPCTL.bit.QUALSEL = 0;//窗口滤波Comp1Regs.COMPCTL.bit.CMPINV = 0;//反转输出Comp1Regs.COMPCTL.bit.COMPSOURCE = 0;//comp1b(+)连接到内部DACComp1Regs.DACCTL.bit.DACSOURCE = 0;Comp1Regs.DACVAL.bit.DACVAL = 465;// 1.5VEDIS;

ePWM模块部分:

EALLOW;EPwm1Regs.TBPRD = 60000;// Set timer periodEPwm1Regs.TBPHS.all = 0;// Phase is 0EPwm1Regs.TBCTR = 0;// Setup TBCLKEPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;// Count upEPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE;// when sync comes, TBCTR=TBPHSEPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // These bits select the source of the EPWMxSYNCO signal. 0 means EPWMxSYNC// TB_SYNC_IN=0EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0 ;// Clock ratio to SYSCLKOUTEPwm1Regs.TBCTL.bit.CLKDIV = 0;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;// Load registers every ZEROEPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;// Setup compareEPwm1Regs.CMPA.half.CMPA = 50; // 40/8*(10^7) = 500nsEPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;// Set PWM1A on CAU当CTR=0时,强制EPWM1A输出高电平EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//当CTR=CMPA且计数器CTR增计数时,强制EPWM1A输出低电平EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module 用于EPWMxA输出上升沿延迟及EPWMxB输出下降沿延迟的死区均被使能。// 延迟输入信号由DBCTL[IN_MODE]字段决定,默认EPWMxA作为下降沿与上升沿延迟的输入源。EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;// Active Hi complementary 高电平互补(AHC)模式:EPWMxB反向。EPwm1Regs.DBRED = 4;// 上升沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DBFED = 14;// 下降沿延迟计数器(这是一个10位的计数器)EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT;// DCAH = Comparator 1 output DCAH的电平高低由比较器1的输出决定EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI;EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1;//EPwm1Regs.DCACTL.bit.EVT1SYNCE = 1;//EDIS;

我将COMP1比较器的反相输入端配置为DAC输入,正相输入端为外部模拟引脚输入。当我在正相输入一个高电平的时候,没有产生ePWM1的同步信号。

我想问一下,

1、ePWM的DC模块产生的DCAEVT1.sync 信号是CBC还是OSHT的?

2、比较器输出 怎样触发DCAEVT1.sync 这个信号?我上面的配置方法是正确的吗?

3、如第二个图所示,DCAEVT1.sync不需要其他配置,只要产生了,就可以让ePWM同步吗?

tao lee36:

回复 Brian Wang0:

补充,我尝试过采用配置比较器输出送到epwm的DC模块,在DCAEVT1事件中断中 通过EPwm1Regs.TBCTL.bit.SWFSYNC = 1;来生成pwm同步信号,但是这样从比较器输出动作到产生同步信号的时间太长,实测有500ns左右,其中测试中断响应时间有300ns左右。

下面是我的DCAEVT1事件中断配置代码:

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT;// DCAH = Comparator 1 output DCAH的电平高低由比较器1的输出决定EPwm1Regs.DCTRIPSEL.bit.DCALCOMPSEL = DC_TZ2;// DCAL = TZ2DCAL的电平高低由TZ2决定EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI;// DCAEVT1 =DCAH High(will become active as Comparator output goes high)// DCAH高电平时产生DCAEVT1事件EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1;// DCAEVT1 = DCAEVT1 (not filtered) 无滤波EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC;//EDIS;EALLOW;EPwm1Regs.TZEINT.bit.DCAEVT1 = 1;// DCAEVT1事件中断使能EDIS;

我想是不是有不进中断直接比较器输出同步ePWM的方法?这样的话,比较器输出到产生同步信号中间的延迟时间是不是会小很多。

TI中文支持网

TI中文支持网